# COMPACT LOW-POWER 2.4 GHz QPSK MODULATOR IN CMOS

### Ahmed M. El-Gabaly and Carlos E. Saavedra

Microwave Integrated Circuits Laboratory, Electrical and Computer Engineering, Queen's University, 19 Union St, Kingston, ON, K7L 3N6 Canada; Corresponding author: ahmed.elgabaly@ece.queensu.ca

Received 3 September 2008

**ABSTRACT:** A compact low-power QPSK modulator is proposed for shortrange wireless communications using a new pass-transistor logic circuit. It is experimentally demonstrated in the unlicensed 2.4 GHz ISM frequency band using standard 0.18 μm CMOS technology, with the data rates well exceeding 100 Mbps. The core circuit occupies only 505 μm by 435 μm and consumes less than 19 mW from 1.8 V. © 2009 Wiley Periodicals, Inc. Microwave Opt Technol Lett 51: 1344–1348, 2009; Published online in Wiley InterScience (www.interscience.wiley.com). DOI 10.1002/mop.24300

**Key words:** *digital modulation; quadrature phase shift keying; CMOS; microwave integrated circuits; short-range wireless communications*

## 1. INTRODUCTION

Gigahertz-range quadrature phase shift-keying (QPSK) modulators have been studied extensively in the literature [1-6]. Most of the reported work generates quadrature signals using frequency divide-by-two circuits (DTCs) [1, 2], or resistor-capacitor, capacitor-resistor (RC-CR) networks with several cascaded stages of amplitude limiters [5–7]. This is usually followed by a pair of Gilbert-cell mixers and a summing junction to modulate and combine the quadrature carriers [1–4, 7, 8]. Such an approach can significantly augment the Integrated Circuit (IC) size, cost, and power consumption. In addition, some of the work was demonstrated in more expensive technologies such as Gallium Arsenide (GaAs), Silicon Bipolar, or BiCMOS.

In this article, a novel CMOS QPSK modulator is proposed using a Pass-Transistor Logic (PTL) network. A major advantage of this topology is its moderate circuit complexity and power consumption compared with other modulators. The concept proposed here builds on our previous work in Ref. 9, but we introduce a new structure and PTL circuit that offers significant improvements in size, power, modulation accuracy, and data rates [10]. The proposed circuit is experimentally demonstrated by directly modulating a 2.4 GHz signal. An accurate phase and amplitude balance is achieved after tuning the 90° phase shifter, with the errors being less than 1.4° and 0.3 dB, respectively. The measured data rates for this modulator reach the 200 Mbps range, whereas the carrier rejection achieved is more than 32 dB. The IC is implemented using a standard 0.18 µm CMOS process, measuring 720 µm by 888 µm and consuming 34 mW of power from a 1.8 V supply. This includes an active input balun and an output buffer integrated on-chip, without which the core circuit area is only 505  $\mu$ m by 435  $\mu$ m, and the estimated power consumption is less than 19 mW. The modulator is suitable for future short-range lowpower wireless applications using either a direct-conversion architecture with a 2.4 GHz carrier or in a heterodyne architecture with a 38 GHz carrier as in point-to-point radio, for example, and a 2.4 GHz intermediate frequency (IF).

Whereas, QPSK modulation is predominantly used in heterodvne radio architectures, this modulation scheme is also convenient for use in direct-conversion radio systems because its moderate complexity enables the design of very high data rate demodulators at the carrier frequency. A well-known merit of direct-conversion transceivers is the absence IF oscillators, bandpass filters, and amplifiers, which substantially reduces the size and power consumption of the IC's in the physical layer. Furthermore, very high data rates are possible with the direct-conversion approach since the frequency bandwidth is no longer limited by a relatively low IF. However, direct-conversion transmitters can suffer from injection pulling, i.e., corruption of the carrier local oscillator (LO) frequency by the power amplifier (PA) output. Such a problem can be alleviated nonetheless by various shielding techniques to isolate the carrier LO [11-13] or by offsetting the LO frequency [14].

The article is organized as follows: Section 2 describes the principle operation and design of the circuit, Section 3 discusses the experimental results, and Section 4 concludes the work.

## 2. CIRCUIT ARCHITECTURE AND DESIGN

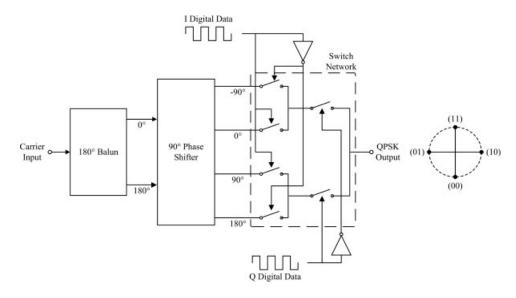

A block diagram of the QPSK modulator is shown in Figure 1. It consists of the following: (1) a  $180^{\circ}$  balun, (2) a  $90^{\circ}$  phase shifter, and (3) a switch network. The  $180^{\circ}$  balun and the  $90^{\circ}$  phase shifter

Figure 1 Block diagram of proposed QPSK modulator

generate all four quadrature phases of the carrier:  $0^{\circ}$ ,  $-90^{\circ}$ ,  $90^{\circ}$ , and  $180^{\circ}$ . Only one of these is selected in the switch network according to both in-phase (*I*) and quadrature-phase (*Q*) digital data, which constitute the QPSK symbol value. In effect, the circuit performs QPSK modulation with the signal constellation shown in Figure 1. This architecture requires only one balun and no summing junction compared with our previous work [9], saving significant space and power. Furthermore, the parasitic coupling and nonidealities associated with the summing junction are no longer present, enabling higher modulation accuracy and data rate [10].

An active common-gate/common-source (CG-CS) pair balun [9, 10, 15] is integrated in the QPSK modulator IC to create differential signals from the off-chip single-ended oscillator. Active baluns are more easily integrated than passive baluns such as centre-tapped transformers [16–19], which can be prohibitively large in the S-band frequency range. The CG-CS active balun also exhibits a low input reflection coefficient and a good phase and amplitude match over a wide band of frequencies [9, 10, 15]. The outputs of the balun are also buffered using source followers to sufficiently drive the following 90° phase shifter with relatively low impedance [10]. Note that the QPSK modulator can also be used directly with the on-chip differential oscillator commonly found in integrated transmitters without the need for a balun.

#### 2.1. Quadrature Phase Shifter

The QPSK modulator signal constellation accuracy and modulation bandwidth depends highly on the accuracy of creating quadrature phases. For this reason, several techniques have been developed over time to generate accurate 90° phase shifters with low phase and amplitude errors. These include the following: (1) frequency divide-by-two circuits (DTCs) [1, 2, 20]; (2) resistorcapacitor, capacitor-resistor (RC-CR) networks [4-6]; (3) resistorcapacitor (RC) all-pass filters [3, 21]; (4) inductor-capacitor (LC) high- and low-pass filters [22–24]; and (5) RC polyphase networks [25–29].

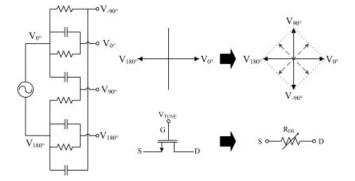

A single-stage tunable RC polyphase network is used in this design due to its small IC footprint and zero DC power consumption compared with the other networks. It also has less signal loss than using two RC-CR circuits, as it combines the two balanced signals as opposed to splitting each signal separately. Figure 2 shows the polyphase network and how it operates [10]. It generally has an all-pass frequency response (unity gain) while shifting the differential inputs by  $\pm 45^{\circ}$  toward each other at the 1/(RC) cut-off frequency and forming the required differential quadrature phases upon combination at the outputs. Therefore, for the relatively high S-band frequency range, a small RC product is required allowing small resistors and capacitors to be used. However, integrated

Figure 2 RC polyphase network and NMOS FET resistor operation

polysilicon resistors can generally exhibit large tolerances (on the order of 20% or more) for small footprints and low resistance values (less than 1 k $\Omega$ ). Such high tolerances are critical since discrepancies will change the cutoff frequency, introducing phase errors at the frequency of interest. For this reason, a variable resistor in the form of a zero-biased NMOS transistor is used, with the resistance controlled by the gate voltage  $V_{\text{TUNE}}$  (Fig. 2). This way the cutoff frequency can now be tuned to the carrier frequency after process variations for the lowest possible phase error.

The effective resistance  $R_{DS}$  of the zero-biased NMOS device is well-known to be approximately given by the following:

$$R_{\rm DS} = \left(\frac{\partial I_{\rm DS}}{\partial V_{\rm DS}}\right)^{-1} \approx \frac{1}{\mu_{\rm n} C_{\rm ox} \frac{W}{L} (V_{\rm GS} - V_{\rm T})} = \frac{1}{\mu_{\rm n} C_{\rm ox} \frac{W}{L} (V_{\rm TUNE} V_{\rm T})} \quad (1)$$

where,  $\mu_n$  is the electron mobility,  $C_{ox}$  is the gate oxide capacitance per unit area, W and L are the width and length of the transistor,  $V_{GS}$  is the gate-source voltage and  $V_T$  is the threshold voltage. It is clear that the resistance is inversely proportional to the tuning voltage and gate width, thus a large voltage or width can be used to yield a relatively low resistance. However, a larger device width will increase the parasitic capacitances, leading to a higher signal loss and degrading the performance. For this reason, the gate width is made narrow while the tuning voltage is increased in proportion for the same resistance. The larger gate overdrive voltage also helps to extend the linearity of the transistor and reduce signal distortion [10].

The cutoff frequency of the polyphase network (1/(RC)) was chosen to be 2.4 GHz for this QPSK modulator. This is an unlicensed ISM frequency band widely used for wireless communication devices. The capacitance *C* in the polyphase network was set to a relatively small value of 0.1 pF to minimize its IC footprint. With *C* = 0.1 pF, the required resistance is *R* = 660  $\Omega$ . An NMOS FET with a narrow gate width of *W* = 1.5  $\mu$ m is used to implement this resistance with a low parasitic capacitance. For the 0.18  $\mu$ m CMOS technology used, the device parameters are as follows:  $\mu_n = 4.38 \times 10^{-2} \text{ m}^2/\text{Vs}$ ,  $C_{ox} = 8.03 \times 10^{-3} \text{ F/m}$ ,  $V_T$ = 0.475 V and *L* = 0.18  $\mu$ m. Therefore, from (1), the required tuning voltage is  $V_{\text{TUNE}} = 0.99 \text{ V}$ . An S-parameter simulation was also run to verify this, indicating a resistance value of about 650  $\Omega$ .

The differential quadrature outputs  $V_{-90}$ ,  $V_0$ ,  $V_{90}$ , and  $V_{180}$  of the RC polyphase network (Fig. 2) are amplified using commonsource amplifiers. This isolates the RC polyphase network from the following switch network, presenting consistent loading impedance to the four outputs regardless of the switching state to ensure good quadrature phase and amplitude match.

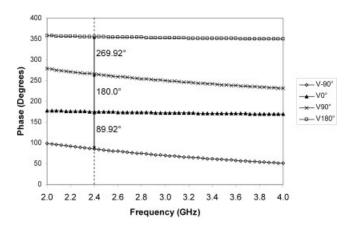

An S-parameter simulation was run to verify the performance of the RC polyphase network, and the phase of the resulting transmission coefficients is plotted in Figure 3. As shown, the phase differences between the outputs are very close to the desired 90°, 180°, and 270° (-90°) at 2.4 GHz, with a phase error of less than 0.08°. The magnitudes of these transmission coefficients also indicate a low amplitude imbalance of 0.071 dB at the same frequency.

#### 2.2. Switch Network

The purpose of the switch network is to pass one signal from the four differential quadrature signals ( $V_{-90}$ ,  $V_0$ ,  $V_{90}$ , and  $V_{180}$ ), whereas blocking the other three, according to both *I* and *Q* data values which constitute the QPSK symbol. In particular, the following digital logic should be realized by the switch network to

Figure 3 Simulated transmission coefficient phase for RC polyphase network at 2.4 GHz

yield the desired QPSK signal constellation at the output  $(V_{\rm QPSK})$  as follows:

$$V_{\text{QPSK}} = IQV_{-90} + IQV_0 + IQV_{90} + IQV_{180} = Q(IV_{-90} + IV_0) + Q(IV_{90} + IV_{180})$$

(2)

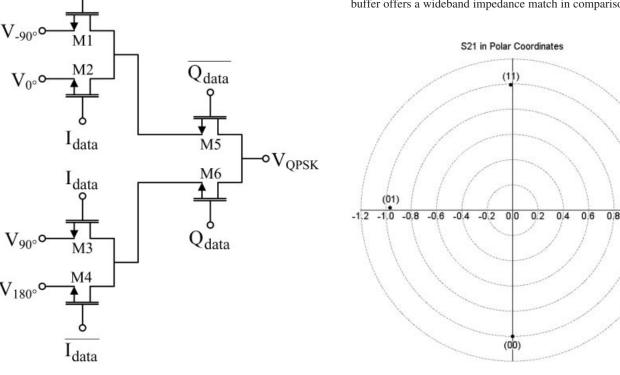

This is realized in Figure 1 as a set of six complimentary switches in two stages, the first four being for the I data stream and the remaining two for the Q data stream. A Pass-Transistor Logic (PTL) circuit consisting of six NMOS switches, as shown in Figure 4, is used to implement this, which has the advantages of small footprint, zero DC power consumption, and high-speed operation. In the ON state, the device can be characterized with the on-

I<sub>data</sub>

Figure 5 Photograph of the QPSK modulator IC

resistance given by (1), where the applied gate-source voltage  $V_{GS}$  is equal to the supply voltage  $V_{DD}$ .

While increasing the FET width W will reduce its on-resistance and thus the signal loss across it, it will also increase its parasitic capacitances. This leads to more capacitive coupling between the data and carrier signals as well as less isolation in the OFF state, adversely affecting the performance of the QPSK modulator. Therefore, a narrow gate width of  $W = 1.5 \ \mu m$  was chosen for this design to minimize this effect, especially at higher data rates where it is more pronounced. To maintain circuit symmetry with respect to the *I* and *Q* data inputs, transistors M5 and M6 are made twice as wide as transistors M1–M4 with  $W = 3 \ \mu m$ .

The QPSK signal output  $V_{\text{QPSK}}$  of the PTL circuit (Fig. 4) is buffered using a source follower to sufficiently drive the external 50  $\Omega$  load with a low insertion loss and reflection coefficient. The buffer offers a wideband impedance match in comparison to using

Figure 4 Circuit schematic of PTL circuit for QPSK modulator

(10)

1.0

1.2

**Figure 7** Measured input  $S_{11}$  and output  $S_{22}$  reflection coefficient

a narrowband passive network which would also be prohibitively large in this frequency range.

# 3. EXPERIMENTAL RESULTS

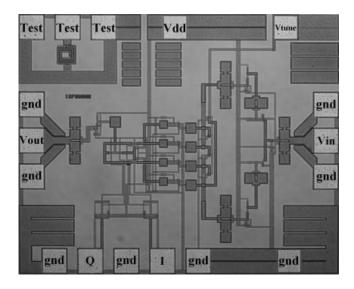

The QPSK modulator was fabricated in a standard (six-metal, single-poly) 0.18  $\mu$ m CMOS process. A photograph of the IC is shown in Figure 5. It occupies a die area of about 0.720 × 0.888 mm<sup>2</sup>, including bonding pads, and consumes 34 mW of power from a 1.8 V supply. Without the input balun and the output buffer, the core circuit area is only 0.505 × 0.435 mm<sup>2</sup> and the estimated power consumption is less than 19 mW.

The first measurement performed was the static constellation of the modulator with the *I* and *Q* data switches held at constant values corresponding to the four QPSK symbols (00, 10, 11, and 10). A polar plot of the normalized transmission coefficient  $S_{21}$  at 2.4 GHz in each of the four states is shown in Figure 6. The maximum phase and amplitude errors are only 1.4° and 0.3 dB, respectively. In addition, the magnitude of this transmission coefficient indicates a maximum loss of less than 5.5 dB. These measurements were performed with the tuning voltage  $V_{\text{TUNE}}$  set to about 0.7 V, as this was found to give the smallest errors at 2.4 GHz. The measurements also reasonably agree with the simulations.

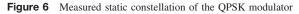

The input  $S_{11}$  and output  $S_{22}$  reflection coefficients were also measured and a plot of their magnitude is shown in Figure 7. At the centre frequency of 2.4 GHz, the input and output reflection coefficients are less than -10 and -17 dB, respectively. These results are sufficiently low as desired, agreeing closely with our simulations.

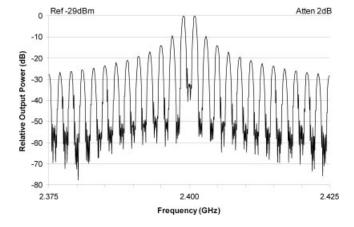

Figure 9 Measured output QPSK spectrum for 100 Mbps

To measure the QPSK modulator's carrier rejection, the same square wave is applied to both *I* and *Q* data channels and the output frequency spectrum is examined. The frequency of the square wave  $f_{MOD}$  was chosen to be 1 MHz. This corresponds to a 2 Mbps data rate per channel or a total throughput of 4 Mbps. The spectrum of an ideal periodic square wave has nonzero components only at the odd-order harmonics of the fundamental frequency (1, 3, 5 MHz, etc.), featuring a sinc-shaped amplitude envelope. Figure 8 shows the output signal spectrum with a frequency span of 50 MHz. The depicted spectrum shape is as expected and the 2.4 GHz carrier is well suppressed by more than 30 dB relative to the main lobes at 2.4 GHz  $\pm 1$  MHz. The carrier input power for this test was set to -20 dBm. For a higher input power of -10 dBm, the carrier rejection remains largely unchanged at about 28 dB.

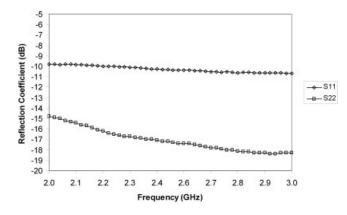

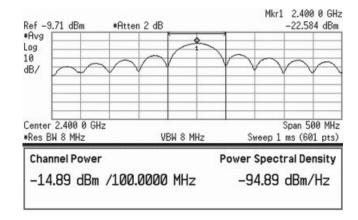

Tests were also performed using pseudo-random binary sequences (PRBS) for the input *I* and *Q* channels. The sequences were encoded in the non-return-to-zero (NRZ) format with rectangular pulses. Their data rate  $f_{MOD}$  was maximized to 50 and 100 Mbps for a total data throughput of 100 and 200 Mbps, respectively. Figures 9 and 10 show the resulting output signal spectra with a centre frequency of 2.4 GHz and frequency spans of 500 MHz and 1 GHz, respectively. It is evident that the circuit operates as a QPSK modulator with its generated spectra closely matching the theoretical one without pulse shaping. Finally, the measured output power is about -15 dBm for -10 dBm input power as indicated on the plots.

Table 1 summarizes the measured characteristics of the QPSK

Figure 8 Measured carrier rejection with 1 MHz square wave

Mkr1 2.400 GHz Ref -12.11 dBm #Atten 2 dB 25.594 dBm #Avg Log 10 dB Center 2.400 GHz Span 1 GHz Res BW 8 MHz #VBW 8 MHz Sweep 1.68 ms (601 pts) **Channel Power Power Spectral Density** -14.88 dBm /200.0000 MHz -97.89 dBm/Hz

Figure 10 Measured output QPSK spectrum for 200 Mbps

modulator IC.

TABLE 1

Summary of Measured Characteristics of QPSK

Modulator IC

IC

| Characteristic    | Results                           |

|-------------------|-----------------------------------|

| Circuit area      | $0.505 \times 0.435 \text{ mm}^2$ |

| DC power          | 19 mW from 1.8 V                  |

| Carrier frequency | 2.4 GHz                           |

| Accuracy          | Amplitude error $\leq 0.3$ dE     |

|                   | Phase error $\leq 1.4^{\circ}$    |

| Insertion loss    | ≤5.5 dB                           |

| Return loss       | Input: ≥10 dB                     |

|                   | Output: ≥17 dB                    |

| Carrier rejection | ≥30 dB                            |

| Data throughput   | Nominal: 100 Mbps                 |

|                   | Maximum: 200 Mbps                 |

| Output power      | -15 dBm                           |

## 4. CONCLUSIONS

A compact low-power QPSK modulator has been proposed in CMOS for short-range wireless applications. An RC polyphase network is employed to generate balanced quadrature signals for its small footprint and zero DC power consumption, with variable NMOS resistors tuned after fabrication to minimize phase errors. Only one of the four differential quadrature signals is selected by a new PTL circuit according to both I and Q digital data, thus eliminating the need for a summing junction. The circuit is demonstrated at 2.4 GHz in a standard 0.18  $\mu$ m CMOS process, with the data rates reaching 200 Mbps and the carrier rejection exceeding 30 dB. An accurate phase and amplitude balance is achieved with the errors being less than 1.4° and 0.3 dB, respectively. The insertion loss is also lower than 5.5 dB, whereas the input and output return losses are better than 10 dB. The core circuit occupies an area of only  $0.505 \times 0.435 \text{ mm}^2$  and consumes less than 19 mW of power.

# ACKNOWLEDGMENTS

The authors would like to acknowledge the products and services provided by the Canadian Microelectronics Corporation (CMC) that facilitated this research, including the IC design tools and fabrication services.

# REFERENCES

- P. Eloranta and P. Seppinen, Direct-digital RF modulator IC in 0.13μm CMOS for wide-band multi-radio applications, IEEE Int Solid State Circ Conf, San Francisco, CA (2005), 532–533.

- J. Itoh, M. Nishitsuji, O. Ishikawa, and D. Ueda, 2.1GHz Directconversion GaAs quadrature modulator IC for W-CDMA base station, IEEE Int Solid State Circ Conf, San Francisco, CA (1999), 226–227.

- A. Boveda, F. Ortigoso, and J. Alonso, A 0.7-3 GHz GaAs QPSK/ QAM direct modulator, IEEE J Solid State Circ 28 (1993), 1340– 1349.

- T. Tsukahara, M. Ishikawa, and M. Muraguchi, A 2-V 2-GHz Sibipolar direct-conversion quadrature modulator, IEEE J Solid State Circ 31 (1996), 263–267.

- K. Yamamoto, K. Maemura, N. Andoh, and Y. Mitsui, A 1.9-GHzband GaAs direct-quadrature modulator IC with a phase shifter, IEEE J Solid State Circ 28 (1993), 994–1000.

- A. Teetzel, A stable 500 to 4000 MHz GaAs IQ modulator IC, IEEE Int Solid State Circ Conf (1997), 364–365.

- B. Razavi, Architectures and circuits for RF CMOS receivers, IEEE Custom Integr Circ Conf, San Francisco, CA (1999), 197–204.

- B. Gilbert, A precise four-quadrant multiplier with subnanosecond response, IEEE J Solid State Circ 3 (1968), 365–373.

- 9. A. El-Gabaly, B. Jackson, and C. Saavedra, An L-band direct-digital

QPSK modulator in CMOS, URSI Int Symp Signals Syst Electron (2007), 563–566.

- A.M. El-Gabaly, Radio frequency direct-digital QPSK modulators in CMOS technology, M.Sc. Thesis, Queen's University, Kingston, ON, Canada, 2007.

- J. Durec, An integrated silicon bipolar receiver subsystem for 900-MHz ISM band applications, IEEE J Solid State Circ 33 (1998), 1352–1372.

- N. Checka, D. Wentzloff, A. Chandrakasan, and R. Reif, The effect of substrate noise on VCO performance, IEEE Radio Freq Integr Circ Symp, Long Beach, CA (2005), 526–526.

- T. Liu and E. Westerwick, 5-GHz CMOS radio transceiver front-end chipset, IEEE J Solid State Circ 35 (2000), 1927–1933.

- B. Razavi, RF transmitter architectures and circuits, IEEE Custom Integr Circ Conf (1999), 197–204.

- C. Saavedra and B. Jackson, Voltage-variable attenuator MMIC using phase cancellation, IEE Proc Circ Devices Syst 153 (2006), 442–446.

- J. Long and M. Copeland, A 1.9 GHz low-voltage silicon bipolar receiver front-end for wireless personal communication systems, IEEE J Solid State Circ 30 (1995), 1438–1448.

- H. Chen, et al., A novel LNA-mixer design with on-chip balun, IEEE Int Symp Circ Syst (2006), 4971–4974.

- J. Long, A low-voltage 5.1-5.8-GHz image-reject downconverter RF IC, IEEE J Solid State Circ 35 (2000) 1320–1328.

- J. Long, Monolithic transformers for silicon RF IC design, IEEE J Solid State Circ 35 (2000), 1368–1382.

- J. Itoh, et al, A low distortion GaAs quadrature modulator IC, IEEE Radio Freq Integr Circ Symp, Baltimore, MD (1998), 55–58.

- S. Altes, T. Chen, and L. Ragonese, Monolithic RC all-pass networks with constant-phase-difference outputs, IEEE Trans Microwave Theory Tech 34 (1986), 1533–1541.

- R. Garver, Broad-band diode phase shifters, IEEE Trans Microwave Theory Tech 20 (1972), 314–323.

- C. Suckling, R. Pengelly, and J. Cockrill, S-band phase shifter using monolithic GaAs circuits, IEEE Int Solid State Circ Conf, San Francisco, CA (1992), 134–135.

- I. Telliez, et al., A compact, monolithic microwave demodulatormodulator for 64-QAM digital radio links, IEEE Trans Microwave Theory Tech 39 (1991), 1947–1953.

- M. Gingell, Single sideband modulation using sequence asymmetric polyphase networks, Electr Commun 48 (1973), 21–25.

- F. Behbahani, Y. Kishigami, J. Leete, and A.A. Abidi, CMOS mixers and polyphase filters for large image rejection, IEEE J Solid State Circ 36 (2001), 873–887.

- M. Borremans, M. Steyaert, and T. Yoshitomi, A 1.5 V, wide band 3GHz, CMOS quadrature direct up-converter for multi-mode wireless communications, IEEE Custom Integr Circ Conf (1998), 79–82.

- P. Khannur and K. Ling, A 2.45GHz fully-differential CMOS imagereject mixer for bluetooth application, IEEE Radio Freq Integr Circ Symp, Seattle, WA (2002), 439–442.

- E. Tiiliharju and K. Halonen, A 0.75-3.6GHz SiGE direct-conversion quadrature-modulator, Eur Solid State Circ Conf (2003), 565–568.

© 2009 Wiley Periodicals, Inc.

# HYBRID IPO-BI-FEM FOR THE ANALYSIS OF 2D LARGE RADOME WITH COMPLEX STRUCTURE

## Hongfu Meng and Wenbin Dou

State Key Laboratory of Millimeter Waves, Southeast University, Nanjing 210096, Peoples Republic of China; Corresponding author: menghongfu@163.com

Received 9 September 2008

**ABSTRACT:** In this article, the iterative physical optics-boundary integral-finite element method (IPO-BI-FEM) is proposed for the analysis of