# A Wideband and High-Linearity *E*-Band Transmitter Integrated in a 55-nm SiGe Technology for Backhaul Point-to-Point 10-Gb/s Links

David del Rio, Graduate Student Member, IEEE, Iñaki Gurutzeaga, Ainhoa Rezola, Juan F. Sevillano, Member, IEEE, Igone Velez, Member, IEEE,

Sten E. Gunnarsson, Member, IEEE, Nataly Tamir, Carlos E. Saavedra, Senior Member, IEEE, José Luis Gonzalez-Jimenez, Senior Member, IEEE,

Alexandre Siligaris, Cédric Dehos, and Roc Berenguer, Senior Member, IEEE

Abstract—This paper presents the design of a wideband and high-linearity E-band transmitter integrated in a 55-nm SiGe BiCMOS technology. It consists of a double-balanced bipolar ring mixer which upconverts a 16-21-GHz IF signal to the 71-76- and 81-86-GHz bands by the use of a 55/65-GHz local oscillator signal, followed by a broadband power amplifier which employs 2-way output power combining using an integrated low-loss balun transformer. The transmitter exhibits an average conversion gain of 24 dB and 22 dB at the 71-76- and 81-86-GHz bands, respectively, with an output 1-dB compression point greater than 14 and 11.5 dBm at each band. A maximum output power of 16.8 dBm is measured at 71 GHz. The dc power consumption is 575 mW. The presented transmitter is used to demonstrate the transmission of a 10.12-Gb/s 64 quadrature amplitude modulated signal with a spectral efficiency of 5.06 bit/s/Hz, which makes it suitable for use in future highcapacity backhaul and fronthaul point-to-point links.

*Index Terms*—BiCMOS, *E*-band, integrated circuits (ICs), millimeter waves, mixer, power amplifier (PA), SiGe, 64 quadrature amplitude modulation (QAM), wireless communications.

## I. INTRODUCTION

THE emergence of high-speed portable devices has greatly increased the demand for data bandwidth in wireless

Manuscript received April 29, 2016; revised December 26, 2016 and January 12, 2017; accepted January 23, 2017. Date of publication February 24, 2017; date of current version August 4, 2017. This work was supported in part by the Basque Government under Grant P12013-13 and in part by the European's Community Framework Progam FP7/2007-2013 under Grant 317957, acronym: E3Network. Consortium: Ceit, FhG, Alcatel-Lucent-I, CEA, IXYS San Sebastian, SiR, ST-I, Sivers IMA, OTE. The work of D. del Rio was supported by the Education Department of the Basque Government.

D. del Rio, I. Gurutzeaga, A. Rezola, J. F. Sevillano, I. Velez, and R. Berenguer are with Ceit, 20008 San Sebastian, Spain, and also with the Technological Campus, Electrical, Electronic and Control Engineering Department, Tecnun (University of Navarra), 20018 San Sebastian, Spain (e-mail: ddelrio@ceit.es).

S. E. Gunnarsson was with Sivers IMA, SE-164 40 Kista, Sweden. He is now with Saab Technologies AB, 175 41 Järfälla, Sweden.

N. Tamir is with Sivers IMA, SE-164 40 Kista, Sweden.

C. E. Saavedra is with the Department of Electrical and Computer Engineering, Queens University, Kingston, ON K7L 3N6, Canada.

J. L. Gonzalez-Jimenez, A. Siligaris, and C. Dehos are with CEA-Leti, 38000 Grenoble, France, and also with the Université Grenoble-Alpes, 38054 Grenoble, France.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TMTT.2017.2664833

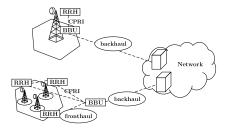

Fig. 1. Fronthaul and backhaul network architecture.

networks. The telecommunications industry responded by introducing 4G/LTE wireless networks nearly half a decade ago. To meet the much higher data traffic flow expected after 2020, standards for a fifth-generation (5G) wireless communications network are being developed [1]. Additionally, it is essential to develop ultrahigh speed mm-wave backhaul links at E-band (71-76 and 81-86 GHz) not only for 5G networks that are at least half a decade away but also for 4G/LTE networks to meet data traffic demands in the immediate future. A concept that has gained much attention in millimeter-wave link design is to move the away from the remote radio heads, as shown in Fig. 1. This allows for a more efficient and dynamic arrangement of the cells, but it implies that the link between the radio head and the baseband processing unit (also known as fronthaul) must carry common public radio interface data, with capacities in the order of 10 Gb/s and very low latency requirements (<1 ms) [2], [3].

There are still important challenges when designing *E*-band integrated transmitter front-ends that need to be addressed. In order to provide full-duplex operation, for example, a wideband design which covers the complete *E*-band is desired, which enables flexible link frequency planning and frequencydivision duplex (FDD) operation. Additionally, to provide the required multi-Gb/s throughput with an efficient channelization that fulfills the ECC and ETSI recommendations [4], [5], high order modulations like 32 or 64 quadrature amplitude modulation (QAM) should be used. In turn, this requires the transmitter to operate at a certain power back-off (typically 7–10 dB), which sets a high linearity requirement throughout the whole bandwidth.

0018-9480 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission.

See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

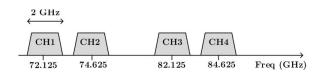

Fig. 2. Considered *E*-band channel distribution.

The interest in multi-Gb/s wireless data links by industry has motivated the design of *E*-band integrated circuits (ICs) using cost-effective CMOS and SiGe BiCMOS technologies from individual circuit blocks to transceiver chip sets [6]–[12]. A packaged SiGe-based transceiver is described in [11] that yields bitrates of up to 20 Gb/s using 32-QAM modulation. It uses different chipsets to cover the 71-76- and 81-86-GHz bands. The transmitter in [10] covers the full *E*-band, yields a bitrate of 3 Gb/s using 64-QAM modulation and it has a saturation output power of 12 dBm. The transceiver in [13] delivers 6 Gb/s with 8-PSK modulation in the 81-86-GHz band using a GaAs mm-wave front-end. The commercial solution reported in [14] transmits up to 3 Gb/s using different chipsets for the 71-76- and 81-86-GHz bands plus an external GaAs power amplifier (PA). Other commercial products based on monolithic microwave ICs and SiGe chipsets are available from companies like Gotmic (Part No. gTSC0023) or Sivers IMA (Part No. FC2121E).

This paper considers a super-heterodyne transmitter with an IF of 17.125/19.625 GHz, a channel bandwidth of 2 GHz and capable of covering the complete *E*-band. It presents the design and measurement results of the mm-wave part of the transmitter circuit: upconverter mixer and PA. This paper is organized as follows. Section II gives the main considerations for the system design. Section III describes the transmitter architecture at block level. Section IV presents the design of the *E*-band upconverter mixer. Section V deals with the design of the PA and Section VI presents the measurement results. Finally, Section VII concludes this paper.

#### II. SYSTEM DESIGN CONSIDERATIONS

## A. Link Requirements and Frequency Plan

The considered transceiver must operate in full-duplex communication mode and provide a data rate of at least 10 Gb/s in each direction in order to meet the requirements of future backhaul and fronthaul links. The chosen duplexing mode is cross-band FDD, using one of the lower (71–76 GHz) and upper (81–86 GHz) bands to transmit in each direction. This way, the TX and RX channels are spaced by at least 10 GHz, which simplifies the design of the diplexer and fulfills the ECC recommendation [4]. Additionally, to avoid crosstalk and interference between closely deployed links, apart from traditional solutions such as different antenna polarization and so on, the bandwidth is divided into four 2-GHz channels as shown in Fig. 2.

#### B. Modulation Scheme

In order to transmit at the required 10-Gb/s rate over a 2-GHz channel, a spectral efficiency of at least 5 b/s/Hz

TABLE I Parameters Considered for the Link Budget Analysis

| Parameter                                               | Value  |

|---------------------------------------------------------|--------|

| Frequency $(f)$                                         | 86 GHz |

| Channel bandwidth $(B)$                                 | 2 GHz  |

| Receiver temperature $(T)$                              | 290 K  |

| Receiver noise figure $(NF_{RX})$                       | 7.5 dB |

| Antenna gain $(G_{ANTENNA})$                            | 52 dBi |

| Diplexer insertion loss $(L_{DIPLEXER})$                | 1 dB   |

| Die to waveguide interconnection loss $(L_{INTERCONN})$ | 2 dB   |

| Other loss $(L_{OTHER})$                                | 4 dB   |

| Coding gain @ BER=10 <sup>-6</sup>                      | 4 dB   |

#### TABLE II

Required  $P_{\text{TX}}$  Versus Rain Rate, to Receive the 64-QAM Signal at 1-km Distance With BER =  $10^{-6}$

| Rain rate (mm/h)       | 0     | 20   | 25   | 30 | 35  | 40 | 45  |

|------------------------|-------|------|------|----|-----|----|-----|

| Minimum $P_{TX}$ (dBm) | -13.4 | -3.3 | -1.6 | 0  | 1.5 | 3  | 4.4 |

is required. In an mm-wave point-to-point link with no significant multipath propagation, a single carrier QAM with a low complexity equalizer provides a good tradeoff between transceiver complexity and performance. Therefore a 64-QAM modulation scheme has been selected for this paper, which allows for the extra overhead introduced by frame headers, coding and root-raised-cosine filter roll-off factor.

The chosen channel bandwidth with such a high spectral efficiency goes beyond the current state-of-the-art considered by the ETSI and therefore the specifications like the spectral mask are not standardized yet [5].

## C. Link Budget

A link budget analysis must be performed to assess the required output power, assuming the link parameters summarized in Table I. The noise power and received signal power at the receiver input are given by (1) and (2), respectively, where k is the Boltzmann constant,  $L_{\rm FS}$  is the free-space loss given by the Friis formula (3),  $L_{\rm ATM}$  is the loss due to atmospheric absorption (0.4 dB/km at the *E*-band) and  $L_{\rm RAIN}$  depends on the rain rate (R) in mm/h and can be calculated using (3) for horizontal polarization (worst case) and 86 GHz [15].

An objective SNR of 26.5 dB is required to obtain a bit error rate of  $10^{-6}$  with 64-QAM modulation [16], which sets the required power at the output of the transmitter ( $P_{TX}$ ). Table II shows the required  $P_{TX}$  to achieve the objective SNR at a distance of 1 km for different rain rates.

$$P_{\text{NOISE}} = 10\log(\text{kTB}) + \text{NF}_{\text{RX}} = -73.47 \text{ dBm}$$

(1)

$$P_{\text{SIGNAL}} = P_{\text{TX}} - 2L_{\text{INTERCONN}} - 2L_{\text{DIPLEXER}} + 2G_{\text{ANTENNA}} - L_{\text{FS}} - L_{\text{ATM}} - L_{\text{RAIN}} - L_{\text{OTHER}}$$

(2)

$$L_{\rm FS} = 92.44 + 20\log(d[\rm km])$$

$$+20\log(f[GHz]) \tag{3}$$

$$L_{\text{RAIN}}[dB/km] = 1.2398R[mm/h]^{0.7006}.$$

(4)

Furthermore, it is necessary to operate the transmitter at a certain back-off below its maximum output power, so as

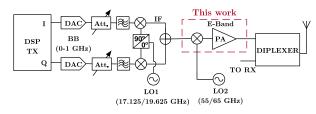

Fig. 3. Architecture of the *E*-band transmitter.

not to distort the signal significantly as well as to reduce the spectral regrowth and fulfill the spectral mask for this kind of link. For 64-QAM, with a roll-off factor of 15%, this back-off requirement is in the order of 9–10 dB below the output 1-dB compression point (OP<sub>1dB</sub>) [17], which sets a high linearity requirement on the PA. Thus, a transmitter with an  $OP_{1dB}$  higher than 14 dBm is required for the considered link. With such a transmitter, according to Table II, it would be possible to transmit 10 Gb/s at 1-km distance for rain rates below 45 mm/h. This rain rate is not exceeded more than 0.01% of the time in a big part of Europe and North America [18].

## **III. TRANSMITTER ARCHITECTURE**

The proposed transmitter has the super-heterodyne architecture shown in Fig. 3. The digital baseband (BB) signal is generated by a field programmable gate array (FPGA) which is connected to two digital-to-analog converters (DAC) that generate the analog in-phase (I) and quadrature (Q) BB signals. The DACs have 14-b resolution and a typical sampling speed of 2.5 Gs/s, which is enough to sample the 0-1-GHz signals and relaxes the stopband requirements of the low-pass filters (they need  $f_{\text{pass}} = 1$  GHz and  $f_{\text{stop}} = 1.25$  GHz). The output connection of the DACs is typically dc-decoupled from the rest of the blocks. This, together with other analog effects like 1/f noise can degrade a portion of the signal located near 0 Hz, which significantly affects the quality of multigigabit signals with high order modulations as described in [19]. To mitigate this effect, a waveform structure with two digital subbands is chosen, centered at -500 and 500 MHz and each with a bandwidth of 1 GHz.

Two variable attenuators are placed to adjust the signal level depending on the DAC output power and to compensate for nonfrequency-selective I/Q amplitude imbalance if necessary. An active I/Q upconverter converts the signal to an IF of 17.125 or 19.625 GHz. This value is selected because it balances the tradeoff between frequency (low enough so as not to complicate the design of the IF blocks) and bandwidth (the required relative bandwidth is below 25%). A second mixer converts the IF signal to the 71-76- or 81-86-GHz bands using a 55/65-GHz local oscillator (LO). This way it is possible to transmit the signal in any of the 4 channels described in Section II. Additionally, with this architecture the mm-wave LO frequency falls far away from the band of interest, which makes the LO feedthrough in the upconverter a less critical issue. It does not affect the saturation of the PA because the gain is much lower at those frequencies, and the remaining spurs are easily filtered out by the diplexer. The PA covers the whole 71-86-GHz band and it must provide enough gain

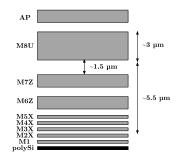

Fig. 4. Simplified metal stack of the BiCMOS 55-nm process.

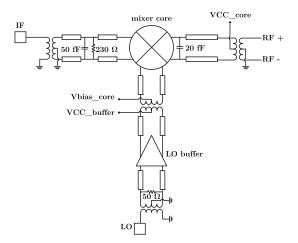

Fig. 5. Block diagram of the *E*-band mixer.

so that the linearity of the transmitter is not limited by the preceding stages.

The following sections will deal with the mm-wave blocks of the transmitter: the mixer and the PA. They are integrated together, as a single IC, in a 55-nm BiCMOS technology provided by STMicroelectronics [20]. The process provides eight copper layers as well as a top aluminum cap, with the simplified stack shown in Fig. 4. The eighth metal layer is ultrathick ( $\sim 3 \mu$ m), sixth and seventh are thick, and first to fifth are thin.

## IV. UPCONVERTER MIXER DESIGN

The mixer upconverts the IF band of 16-21 GHz to 71-76 GHz and 81-86 GHz using LO signals of 55 and 65 GHz, respectively. With the PA having a gain of 25-28 dB, there is sufficient system gain to allow for the use of a semipassive mixer with a conversion loss of approximately 5 dB, without the need for a gain stage. Using the specifications derived in Section II, the target OP<sub>1dB</sub> of the upconverter is at least -5 dBm, which includes a margin of a few dB.

The upconverter block has the architecture shown in Fig. 5 and consists of a double-balanced mixing core, a buffer for the LO signal and the required matching networks and interconnections. The double-balanced topology is selected because of its superior linearity performance and port-to-port isolation. The IF and LO signals are converted from single-ended to differential using integrated transformer baluns. A second set of center-tapped transformers is used to provide dc bias to the

Fig. 6. (a) Schematic of the bipolar ring mixer core. (b) Schematic of the CB LO buffer.

mixer core and to dc decouple it from the LO buffer and the output.

A 50-fF capacitor and a 230- $\Omega$  resistor are placed in shunt with the IF transformer's secondary winding to resonate out its inductance and simultaneously provide a broadband match to 50  $\Omega$  over the 16–21-GHz range. At the RF output port of the mixer, a 20 fF capacitor is used to resonate out the inductance of the RF transformer's primary winding at 78.5 GHz (center of the *E*-band) and to provide the required 71–86-GHz output bandwidth when the secondary is loaded with 50  $\Omega$ (a 50- $\Omega$  interface is chosen between the mixer and the PA). The transmission lines are implemented as side-shielded microstrip lines and the capacitors have a metal-oxidemetal (MOM) structure. The transformers, capacitors and interconnects are simulated using the Momentum electromagnetic (EM) solver.

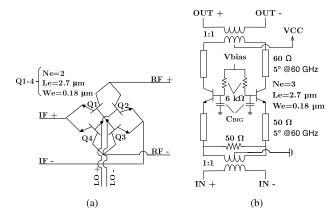

The schematic of the double-balanced mixing core is shown in Fig. 6(a). This topology is chosen for its low power consumption, good linearity and compact layout, at the expense of higher loss than the standard Gilbert Cell [21]. Basic ring mixers, whether diode- or transistor-based, typically exhibit a conversion loss in the range of 9–12 dB and they require large LO signal power levels. In this paper, HBTs are used in the ring because they offer a better input impedance match at the LO port. The used HBTs have two emitter fingers of dimension  $W_e = 0.18 \ \mu \text{m}$  and  $L_e = 2.7 \ \mu \text{m}$ . The transistor cells have been RCc extracted for the simulations. In order to optimize the transistor arrangement and their connections, the transistor cells are removed from the layout, ports are added at the connection points and the resulting structure is EM simulated, following a procedure similar to the one outlined in [7]. Fig. 7 shows the 3-D view of the mixer core layout. As observed, the connections are made symmetrical with the objective of minimizing the imbalance between the differential branches and thus reduce the LO feedthrough.

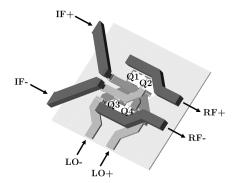

To meet the conversion loss target of 5 dB for the mixer core and to simultaneously keep the LO power requirements at moderately low levels, a dc bias voltage, Vbias\_core, is applied to the base terminals (the LO port) of the transistors. The dc voltage is in the vicinity of the transistors' base-emitter turn-on voltage, so as to place the devices in the most nonlinear

Fig. 7. 3-D view of the mixer core connections.

Fig. 8. CG versus LO voltage at different base bias voltages.

region of their I-V curve, thus leading to stronger mixing tones and lower conversion loss—a technique that has been applied before to MOSFET ring mixers [22].

Fig. 8 shows the simulation of the conversion gain (CG) of the HBT ring mixer as a function of the LO signal amplitude for different values of Vbias\_core. Consider, hypothetically, that the available LO signal amplitude was only 0.2 V which corresponds to -4 dBm in a 50- $\Omega$  environment. For this case, the conversion loss of the mixer without any dc bias applied to the base terminals would fall well below the -40-dB cutoff of the vertical axis in Fig. 8. Yet, the graph shows that if Vbias\_core is set to 700-mV dc, then the mixer's conversion loss can be reduced to -5 dB.

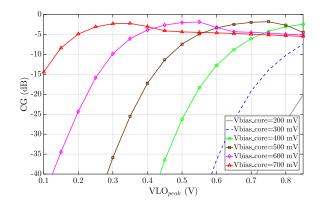

The LO path includes a single-stage common-base (CB) buffer amplifier like the one shown in Fig. 6(b) to boost the LO signal prior to entering the passive mixing core and which is based on [23]. The base terminals are biased from an 850-mV supply through 6-k $\Omega$  resistors and large MOM capacitors are used as RF shorts to ground at the bases. The CB stage draws a current of 8 mA from a collector supply voltage of 1.2 V and exhibits a simulated voltage gain of 12 dB at 55 GHz and 14 dB at 65 GHz, with a maximum output voltage swing of 900 mVp.

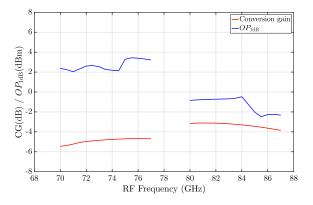

The simulation results of the mm-wave mixer block when loaded with 50  $\Omega$  are shown in Fig. 9, with all the extracted and EM simulated parasitics taken into account. The CG is between -5 and -3 dB for both the lower and upper subbands and the OP<sub>1dB</sub> is better than -3 dBm. The simulated LO-output isolation is 20 dB.

Fig. 9. Postlayout simulated CG and  $OP_{1 \text{ dB}}$  of the mixer when loaded with 50  $\Omega$ .

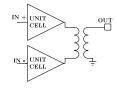

Fig. 10. Block diagram of the power combined PA cells.

## V. POWER AMPLIFIER DESIGN

## A. General Description of the PA Architecture

In order to meet the system requirements given in Sections II and III, the PA must provide a gain bigger than 25 dB and an  $OP_{1dB}$  bigger than 14 dBm, maintaining its performance along the complete *E*-band (71–86 GHz).

The low breakdown voltages of high speed SiGe HBTs, with typical BV<sub>CE0</sub> values of 1.5-1.8 V, limit the maximum voltage swing and thus the achievable output power at mmwave frequencies. The most accepted strategy is to combine the output power of various PA cells [8], [24], [25], where the optimum number of cells to be combined depends on a tradeoff between output power, combining efficiency and routing complexity. The PA presented in this paper consists of two identical single-ended unit cells which are combined at the output as shown in Fig 10. This way around 2 dB higher power than with a single cell can be obtained (assuming a combiner insertion loss (IL) of around 1 dB) and at the same time a balanced input is presented to the mixer. Additionally, with this structure it is easy to make a symmetrical layout and also keep the transistors of both cells in close proximity to increase the matching and minimize the imbalance.

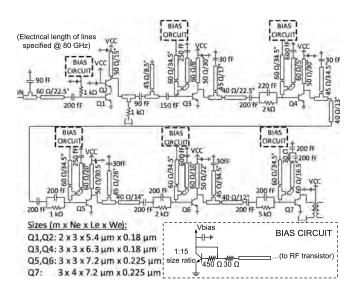

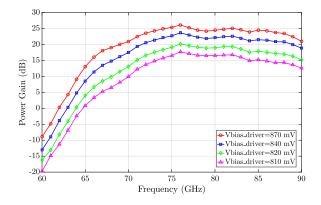

To achieve the required gain, each cell is implemented using a driver in cascode configuration followed by five commonemitter (CE) stages, with the schematic shown in Fig. 11. The transistor sizes are up-scaled toward the output to increase the power handling capabilities of the last stages and maintain a low power consumption at the input stages. The dc bias of the driver stage provides a tuning knob for self-healing purposes, as the gain can be varied to compensate for temperature, process and aging variations, as well as to implement automatic gain control systems. Fig. 12 shows the measured gain variation versus driver bias voltage for a standalone

Fig. 11. Schematic of the designed single-ended unit cell.

Fig. 12. Measured variation of PA gain versus driver dc bias.

version of the PA. As observed, a variation bigger than 8 dB can be obtained by changing the driver bias voltage from 810 to 870 mV.

## B. Output Balun

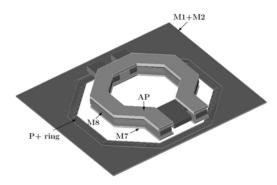

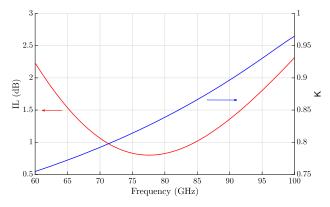

An integrated transformer balun is used to combine the outputs of the two single-ended PA cells, since transformers provide low IL, high coupling coefficient, and compact layout simultaneously at mm-wave frequencies [26]–[28]. The balun is designed to minimize the IL at E-band frequencies and maximize its power combining efficiency. It is implemented on-chip using an octogonal stacked transformer structure like the one shown in Fig. 13. The primary is made using one turn of the ultrathick metal (M8), whereas the secondary is implemented using Alucap and M7 turns connected in parallel at the output. This way a high coupling coefficient (0.8-0.9)can be achieved and the lower M7 turn acts a shield for the primary. A P+ ring is placed around the structure to avoid induced currents spreading through the substrate and coupling to other parts of the circuit. The surrounding ground plane is implemented stacking the first two metals to minimize the resistance and maximize the quality factor. The coupling factor

Fig. 13. 3-D view of the output balun transformer.

Fig. 14. Simulated IL and K of the output balun.

K is calculated as

$$K = \sqrt{\frac{Im(Z12)^2}{Im(Z11) \cdot Im(Z22)}}$$

(5)

and its simulated value is plotted together with the IL in Fig. 14. As shown, the IL is below 1 dB from 71 to 86 GHz, whereas the coupling coefficient is between 0.8 and 0.9.

Once the balun is designed, the connection to the output stage transistor cells is optimized, taking the parasitic inductance due to the length of the connections and the output pad capacitance (47 fF) into account. The arrangement is made as symmetrical as possible so as not to unbalance the output and to load the cells with equal impedances. In order to provide the required output power, each cell is loaded with  $\sim 8 \Omega$ .

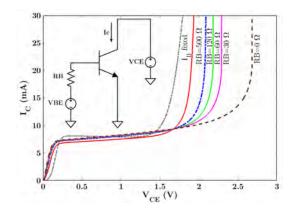

#### C. Power Transistors

The high speed SiGe HBT transistors available in the technology provide  $f_T/f_{MAX}$  of 320/370 GHz, but their BV<sub>CE0</sub> of 1.5 V limits the maximum collector–emitter voltage swing. Nevertheless, if the excess holes generated in the base–collector junction can flow out of the base, then they do not contribute to the avalanche multiplication effect and the breakdown limit can be reliably extended [29], [30]. Fig. 15 shows the simulated  $I_C$  versus  $V_{CE}$  curves of an HBT transistor when it is biased by a fixed  $I_B$  current or by a  $V_{BE}$  dc voltage connected through a resistor (RB). When the base current is fixed, the excess holes cannot flow out of the base and breakdown occurs at a voltage around 1.5 V. On the other hand, if there is a 0- $\Omega$  return path from the

Fig. 15. IC versus VCE with RB as a parameter.

base to the emitter, then the breakdown limit is extended to around 2.5 V (more than x1.6 improvement). For moderate impedances the limit is above 2 V. Additionally, it is observed that the breakdown effect is also dependent on the current density (adjusted varying  $V_{BE}$ ). An increase of the limit is observed at lower  $V_{BE}$  voltages, at the cost of having less current and consequently smaller gain.

Therefore the transistors are biased providing a  $V_{\rm BE}$  voltage through proportional to absolute temperature mirrors and the bias circuits and matching networks are designed to provide a moderate impedance to the transistor bases ( $\sim 50 \Omega$  at dc and  $\sim 20 \ \Omega$  at the *E*-band), which allow reliable operation at a Vcc voltage of 1.7 V. The CE stages are nominally biased at current densities of  $\sim 1-3$  mA/ $\mu$ m<sup>2</sup> that maximize the BV<sub>CE0</sub> and thus the output power. In addition, biasing at low  $V_{\rm BE}$ voltages makes the gain slightly increase when the PA is driven by large power signals, which helps increasing the 1-dB compression point by pushing it toward the saturation point. Special care is placed so that this gain expansion does not significantly degrade the IP3 of the amplifier, which is important when dealing with high-order modulations as 64-QAM. The driver stage is nominally biased at a current density of ~5.5 mA/ $\mu$ m<sup>2</sup> to maximize the gain. The transistors are implemented with different cells in parallel, each with various fingers in Nx(CBEB)-C configuration to minimize the length to width ratio and consequently minimize the parasitic inductance and voltage drop along the fingers. The placement and spacing of the cells is done by carefully taking power management and reliability rules into account. Each cell is RCc extracted and the connections between and to the cells have been EM simulated to optimize the arrangement and to include all the effects introduced by the layout: parasitic capacitances, inductive/resistive degeneration, and so on.

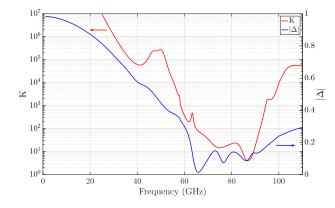

#### D. Stability

Stability is an important issue when designing mm-wave PAs, especially when they have multiple stages. RC networks are placed at the inputs of the CE stages to increase the losses at lower frequencies and reduce the oscillation risk observed at frequencies around 20–30 GHz. The stability of the cascode stage is enhanced by placing a shunt 1-k $\Omega$  resistor at its output.

The simulated K and  $\Delta$  stability factors of the complete PA up to 110 GHz are shown in Fig. 16.

Fig. 16. K and  $|\Delta|$  stability parameters of the PA.

## E. Matching Networks

The matching networks are designed to provide a broad bandwidth in both the gain and linearity of the amplifier. This is achieved by presenting a moderate impedance to the previous stages ( $\sim$ 30–40  $\Omega$ ) which balances the gain and linearity, as well as by tuning the stages at slightly different frequencies to increase the overall bandwidth. The PA input is matched to 50  $\Omega$  to facilitate the integration with the mixer. The matching networks are implemented using transmission lines and MOM capacitors.

The transmission lines are constructed as side-shielded microstrip lines. The first two metals (M1 and M2) are stacked to provide a low-resistivity ground plane and increase the quality factor, with a loss of ~0.6 dB/mm at *E*-band frequencies. The MOM capacitors are custom made using multiple fingers of the top ultrathick and thick metals, which have less resistive losses and lower parasitic capacitance to ground due to their bigger distance to the substrate. In addition, a ground shield with the M1 and M2 layers is placed underneath to further reduce the losses. This way it is possible to achieve high quality factors ( $Q \sim 20$ ) at the band of interest.

Capacitors are placed at the end of the shunt transmission lines to prevent dc shorts. By carefully designing these LC networks, it is possible to provide the required reactance at *E*-band frequencies and simultaneously introduce a transmission zero at 50–60 GHz, which mitigates the effect of the LO feedthrough from the mixer.

The coupling effects between the different passive components are taken into account by EM simulations.

## VI. EXPERIMENTAL RESULTS

## A. On-Wafer Measurement Results

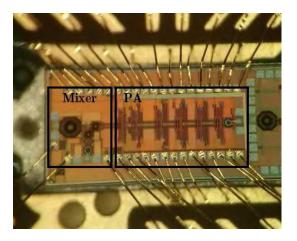

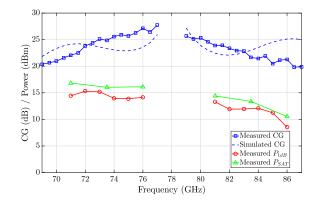

The manufactured die occupies an area of  $1.63 \text{ mm}^2$  and its photograph is shown in Fig. 17. It is attached and wire-bonded to a printed circuit board (PCB) to provide the dc bias to the circuit, whereas on-wafer ground-signal-ground probes are used for the RF signals. The measured and simulated CG of the *E*-band transmitter is shown in Fig. 18. For the measurement, the IF signal is swept between 14 and 22 GHz whereas the LO is set at 55 and 65 GHz with a power of 0 dBm. As shown, an average CG of 23 and 25 dB is measured at the lower band 71.125–73.125- and 73.625–75.625-GHz channels

Fig. 17. Photograph of the fabricated chip.

Fig. 18. Measured CG, P1dB, and Psat versus output frequency.

respectively, with a gain flatness of  $\pm 1.4$  and  $\pm 0.8$  dB across the channel bandwidth. As for the higher subband, the average measured CG is 23 and 21.5 dB at the 81.125–83.125- and 83.625–85.625-GHz channels, respectively, with a flatness of  $\pm 1.5$  and  $\pm 0.7$  dB.

Fig. 18 also shows the measured 1-dB compression point and output saturation power ( $P_{SAT}$ ) versus output frequency. As observed, the  $OP_{1dB}$  is higher than 14 dBm in the lower subband, with a maximum of 15.3 dBm at 72 GHz, and higher than 11.2 dBm in the 81–85-GHz band. With regard to the saturation power, it has a maximum of 16.8 dBm at 71 GHz and it is higher than 12.3 dBm up to 85 GHz. A sharp decrease in the output power is observed at 86 GHz, which is thought to be caused by a mismatch in the impedance presented by the output balun to the last stage at this frequency.

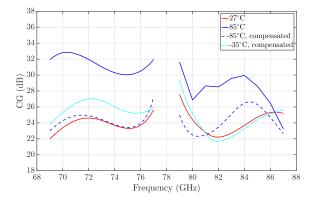

Fig. 19 shows the simulated influence of temperature on the transmitter CG. If the base bias voltages are kept at their nominal values, a significant degradation can be observed, especially at -35 °C (the CG at this temperature falls below the area of the graph because it is around -40 dB). This is caused by the strong dependence of the HBT I-V curve on temperature. However, if an offset of around -1 mV/ °C is applied to the base bias voltages, then the performance can be brought back to the expected range, as shown in the figure (dashed lines). Thus, a linear temperature dependent bias circuit could easily be implemented to compensate for

Fig. 19. Simulated CG versus output frequency as a function of temperature.

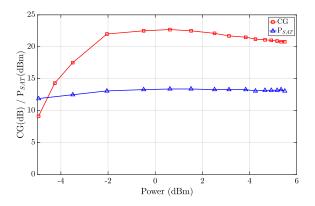

Fig. 20. Measured CG and saturation power versus LO power at 83.5 GHz.

the effect of temperature differences. Similarly, process corner simulations suggest that the effect of process deviations can also be minimized by applying an offset to the bias voltages.

Fig. 20 shows the measured CG and  $P_{SAT}$  as a function of the LO power at 83.5 GHz. The optimum performance in terms of gain and linearity is achieved for an LO power above -2 dBm. As shown, very little variation in  $P_{SAT}$  is obtained because the output power of the transmitter is mainly determined by the PA.

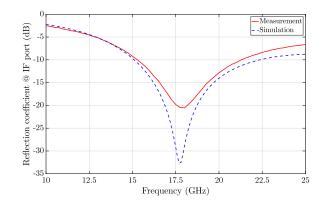

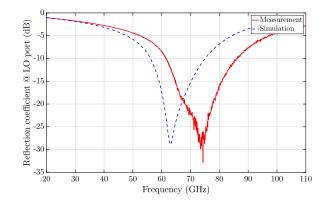

The measured LO feedthrough from the LO input of the mixer to the output of the PA is better than -50 dB at 55 GHz and better than -15 dB at 65 GHz. This feedthrough is thought to be caused by mismatches in the mixer structure as well as by coupling through the substrate and/or the measurement probes. Nevertheless, the obtained value is enough for the intended application because *E*-band diplexers (like the ones supplied by K&L Microwave or MtronPTI, for instance) typically attenuate more than 60 dB the spurs that fall out of the band. The small-signal reflection coefficient at the IF input port has also been measured, obtaining the results depicted in Fig. 21. It is well matched to 50  $\Omega$  at the IF frequency range, with a value lower than -10 dB from 15.2 to 21.3 GHz. As for the matching at the LO port, shown in Fig. 22, it is -6 dBat 55 GHz and -15 dB at 65 GHz. As observed, there is an up-shift in frequency with respect to simulations, which can be compensated by applying a bigger LO power at 55 GHz.

A Vcc value of 1.7 V is used for the PA and mixer, and of 1.2 V for the LO buffer. The base bias voltages are

Fig. 21. Measured small signal reflection coefficient at the IF input.

Fig. 22. Measured small signal reflection coefficient at the LO input.

650 mV for the mixer, 850 mV for the LO buffer and between 800–900 mV for the PA cells. The overall dc consumption of the *E*-band transmitter, under small-signal conditions, is 575 mW. According to what it is presented in Section II, this transmitter can be used to transmit a 64-QAM modulated signal with 2-GHz bandwidth over 1 km distance for rain rates below 45 and 35 mm/h at the lower and upper parts of the *E*-band respectively.

The main performance metrics of the presented transmitter are summarized and compared to other state of the art CMOS and BiCMOS *E*-band transmitters in Table III.

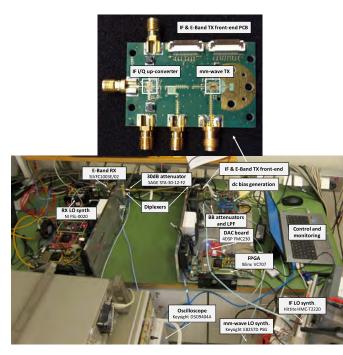

#### B. Multigigabit Signal Transmission Measurements

The performance of the implemented *E*-band transmitter with modulated multigigabit signals has also been evaluated, by means of the loop-back test setup shown in Fig. 23. This setup is intended to emulate the system proposed in Section III. The BB signal to be transmitted is generated using an FPGA (Xilinx VC707), and it consists of two digital subbands with 1 GHz bandwidth centered at -500 and 500 MHz, respectively, as described in Section III. The information in each digital subband is transmitted at a symbol rate of 869.6 Mbaud/s and it is organized in frames, with a short preamble for synchronization and equalization purposes.

The in-phase (I) and quadrature (Q) components of the modulated signal are converted to analog using a 14-bit 2.5-Gs/s DAC board (4DSP FMC230), attenuated (so as to operate the rest of the components in their linear region) and

| TABLE III                                                                  |

|----------------------------------------------------------------------------|

| COMPARISON OF STATE-OF-THE-ART CMOS AND BICMOS <i>E</i> -band Transmitters |

| Reference | Technology          | Output Freq.(GHz) | Input Freq.(GHz) | Avg. Gain(dB) | $P_{1dB}(dBm)$      | $P_{SAT}(dBm)$       | $P_{dc}$   |

|-----------|---------------------|-------------------|------------------|---------------|---------------------|----------------------|------------|

| [9]       | $0.13 \ \mu m$ SiGe | 71-76(chip1)      | Baseband         | 37.5          | 16-17.5             | 18.8-20              | 1.75 W (*) |

|           |                     | 81-86(chip2)      | Baseband         | 37.5          | 15.8-16.5           | 18-18.8              | 1.8 W (*)  |

| [10]      | 40 nm CMOS          | 71-86             | Baseband         | 10            | 7-8.8               | 10-12.5              | 102 mW     |

| [11]      | $0.35 \ \mu m$ SiGe | 71-76(chip1)      | Baseband         | 25            | N/A                 | 15(max)              | 1.6 W (**) |

|           |                     | 81-86(chip2)      | Baseband         | 25            | N/A                 | 15(max)              | 1.6 W (**) |

| This work | 55 nm SiGe          | 71-86             | 16-21            | 23            | 14-15.2(71-76 GHz)  | 16-16.8(71-76 GHz)   | 575 mW     |

|           |                     |                   |                  |               | 8.5-13.3(81-86 GHz) | 10.5-14.4(81-86 GHz) |            |

(\*)Including PLL, I/Q modulator and VGAs. (\*\*)Including VCO.

Fig. 23. Setup used for the loop-back test with a modulated signal.

then low-pass filtered. A custom IC I/Q upconverter is used to convert the signal from 0–1-GHz to 17.125/19.625-GHz IF. As for the introduced frequency selective phase and amplitude I/Q imbalance, it is compensated using digital predistortion following the procedure described in [31]. The implemented SiGe transmitter die is mounted on a PCB together with the I/Q upconverter. A standard FR-4 substrate with two copper layers is used for the dc traces, while a low-loss Rogers RO4350B substrate is attached on top of it for the RF and mm-wave transmission lines. SMA connectors are placed for the BB and IF LO signals. A 1.85-mm connector is used for the 55/65 GHz LO signal, whereas the *E*-band output is fed into a WR-12 waveguide. The FR-4 is removed at the WR-12 opening to minimize the loss.

*E*-band diplexers are placed at the TX output and RX input, connected through a WR-12 waveguide and a 30 dB attenuator (Sage STA-30-12-F2). A commercial *E*-band transceiver (Sivers IMA FC1003E/02) is used to down-convert the signal to a low-IF centered at 1.25 GHz. The received signal is captured using a 4-GHz oscilloscope (Keysight DSO9404A) and then analyzed using a demodulator implemented in MATLAB. This demodulator performs signal acquisition, synchronization, and equalization.

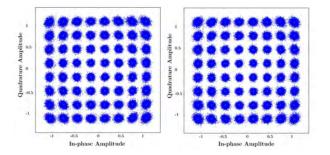

Fig. 24. Obtained constellations (left: lower subband, right: upper subband) when transmitting a 10 Gb/s 64-QAM modulated signal over the 72.125-GHz channel.

TABLE IV Summary of Loop-Back Test Results

| Freq.                               | Bandwidth | Modulation | Bitrate    | EVM      | $P_{OUT}$          |

|-------------------------------------|-----------|------------|------------|----------|--------------------|

| (GHz)                               | (MHz)     |            | $(Gb/s)^1$ | $(\%)^2$ | (dBm) <sup>3</sup> |

|                                     |           | 16-QAM     | 6.74       | 4.5/4.6  |                    |

| 72.125                              | 2000      | 32-QAM     | 8.43       | 4.4/4.4  | 4                  |

|                                     |           | 64-QAM     | 10.12      | 3.5/3.2  |                    |

|                                     |           | 16-QAM     | 6.74       | 3.6/5.5  |                    |

| 74.625                              | 2000      | 32-QAM     | 8.43       | 3.7/5.2  | 4                  |

|                                     |           | 64-QAM     | 10.12      | 3.2/4.5  |                    |

|                                     |           | 16-QAM     | 6.74       | 4.0/6.2  |                    |

| 82.125                              | 2000      | 32-QAM     | 8.43       | 4.4/6.0  | 2                  |

|                                     |           | 64-QAM     | 10.12      | 3.7/5.3  |                    |

|                                     |           | 16-QAM     | 6.74       | 6.1/7.1  |                    |

| 84.625                              | 2000      | 32-QAM     | 8.43       | 6.5/7.9  | 1                  |

|                                     |           | 64-QAM     | 10.12      | 5.3/6.4  |                    |

| $^{1}$ Raw data-rate of the payload |           |            |            |          |                    |

$^{1}$ Raw data-rate of the payload.  $^{2}$ EVM of (Lower/Upper) sub-bands.  $^{3}$  At the PA output.

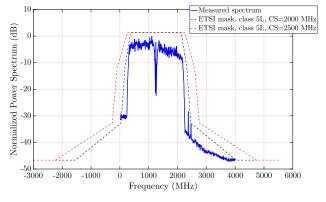

Fig. 24 shows the received constellations when a 10-Gb/s signal is transmitted at the 72.125 GHz channel using 64-QAM modulation. The measured error vector magnitude is 3.5% and 3.2% at the lower and upper digital subbands, respectively. Table IV summarizes the measured performance for the tested channels and modulation schemes. As shown, a maximum bitrate of 10.12 Gb/s is obtained over a 2-GHz bandwidth using 64-QAM modulation, which corresponds to a spectral efficiency of 5.06 b/s/Hz. The output power has a back-off of around 10 dB below the OP<sub>1dB</sub>. Fig. 25 shows the down-converted spectrum (at IF of 1.25 GHz) when the signal is transmitted through the 72.125-GHz channel. The ETSI spectral masks for class 5L (64-QAM) are also shown, extrapolated for a channel separation (CS) of 2000 and 2500 MHz (the CS considered in Section II of this paper). The masks have been extrapolated because class

TABLE V COMPARISON OF STATE-OF-THE-ART MULTIGIGABIT *E***-BAND TRANSMITTERS**

| Reference | Technology | Modulation | Bitrate | Spectral eff. |

|-----------|------------|------------|---------|---------------|

|           | 85         |            | (Gb/ps) | (bit/s/Hz)    |

| [8]       | CMOS       | 64-QAM     | 3       | <6            |

|           |            | QPSK       | 8       | <2            |

| [9]       | SiGe       | 64-QAM     | 0.6     | <6            |

|           |            | 128-QAM    | 0.7     | <7            |

| [11]      | SiGe       | 32-QAM     | 20      | <5            |

| [12]      | SiGe       | QPSK       | 18      | <2            |

| [13]      | GaAs       | 8-PSK      | 6       | 2.4           |

| [32]      | SiGe       | 256-QAM    | 0.04    | <8            |

| [33]      | CMOS       | 1024-QAM   | 0.5     | <10           |

| [34]      | mHEMT      | QPSK       | 10      | <2            |

| [35]      | GaAs       | 16-QAM     | 5       | 3.2           |

| [36]      | GaAs       | 16-QAM     | 10      | 2             |

| ELVA-1    | -          | 256-QAM    | 10      | 5             |

| PPC-10G   |            |            |         |               |

| This work | SiGe       | 64-QAM     | 10.12   | 5.06          |

Fig. 25. Down-converted spectrum together with extrapolated masks for class 5L and CS = 2000 MHz and CS = 2500 MHz.

5L is not completely specified for CS bigger than 750 MHz yet [5]. Some spurs due to clock signal leakage in the FPGA and DAC can be observed, but they do not prevent from fulfilling the mask.

Table V compares the achieved performance with other reported state-of-the-art transmitters. It should be noted that, except the LO signal generators, the rest of the blocks used to generate, upconvert and down-convert the signal are made of custom implemented prototypes and commercial components rather than lab equipment as used in other reported testbenches.

#### VII. CONCLUSION

An integrated mm-wave transmitter has been presented, which can be used for the transmission of multigigabit signals in a proposed E-band point-to-point link for backhaul/fronthaul networks. The transmitter consists of a double-balanced bipolar ring upconverter mixer and a PA with 2-way output power combining. The performance of the implemented device is tested both standalone and together with other custom prototypes and commercial components in a loop-back setup in order to test the transmission of a multigigabit signal. A maximum datarate of 10.12 Gb/s is obtained with a spectral efficiency of 5.06 b/s/Hz. The presented *E*-band transmitter, integrated in a low cost technology,

achieves a very good combination of broad bandwidth and high output power together with the capability of transmitting a spectrally efficient multigigabit signal.

## ACKNOWLEDGMENT

The authors would like to thank M. G. Frecassetti from Alcatel-Lucent-I for the advices regarding the regulatory aspects and A. Pallotta from ST-I for the help regarding the 55 nm BiCMOS technology.

#### REFERENCES

- [1] K. Moskvitch, "Tactile Internet: 5G and the Cloud on steroids" IET Eng. Technol. Mag., vol. 10, no. 4, pp. 48-53, 2015.

- [2] J. Segel and M. Weldon, "Lightradio whitepaper 1: Technical overview," Alcatel-Lucent, Boulogne-Billancourt, France, Tech. Rep., 2011.

- [3] D. Mavrakis, C. White, and F. Benlamlih, "Last mile backhaul options for West European mobile operators," Informa Telecoms & Media, London, U.K., Tech. Rep., 2010. [Online]. Available: http://cbnl.com/sites/all/files/userfiles/files/Last-Mile-Backhaul-Optionsfor-West-European-Mobile-Operators.pdf

- [4] SMT-Ready E-Band Radio Frontend Reference Design. Doc. B132-I0128-V1-7600-EU-EC-P, Infineon Technol. AG, Apr. 2015.

- [5] Specific Attenuation Model for Rain for use in Prediction Methods, Doc. ITU-R P.838-3, 2005.

- [6] B. Sheinman et al., "An active up conversion mixer covering the entire 71-86 GHz E-band range in SiGe technology," in Proc. IEEE Int. Conf. Microw., Commun., Antennas Electron. Syst. (COMCAS), Tel Aviv, Israel, Oct. 2013, pp. 1-4.

- [7] D. del Rio et al., "Layout-aware design methodology for a 75 GHz power amplifier in a 55 nm SiGe technology," Integr., VLSI J., vol. 52, pp. 208-216, Jan. 2016.

- [8] D. Zhao and P. Reynaert, "An E-band power amplifier with broadband parallel-series power combiner in 40-nm CMOS," IEEE Trans. Microw. Theory Techn., vol. 63, no. 2, pp. 683-690, Feb. 2015.

- [9] R. Levinger et al., "High-performance E-band transceiver chipset for point-to-point communication in SiGe BiCMOS technology," IEEE Trans. Microw. Theory Techn., vol. 64, no. 4, pp. 1078-1087, Apr. 2016.

- D. Zhao and P. Reynaert, "A 3 Gb/s 64-QAM E-band direct-conversion [10] transmitter in 40-nm CMOS," in Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC), Nov. 2014, pp. 177-180.

- [11] S. Trotta et al., "A V and E-band packaged direct-conversion transceiver chipset for mobile backhaul application in SiGe technology," in Proc. 44th Eur. Microw. Conf. (EuMC), Oct. 2014, pp. 1655-1658.

- [12] I. Sarkas et al., "An 18-Gb/s, direct QPSK modulation SiGe BiCMOS transceiver for last mile links in the 70-80 GHz band," IEEE J. Solid-State Circuits, vol. 45, no. 10, pp. 1968-1980, Oct. 2010.

- [13] V. Dyadyuk et al., "A multigigabit millimeter-wave communication system with improved spectral efficiency," IEEE Trans. Microw. Theory Techn., vol. 55, no. 12, pp. 2813-2821, Dec. 2007.

- [14] SMT-Ready E-Band Radio Frontend Reference Design, document B132-I0128-V1-7600-EU-EC-P, Infineon Technol. AG, Apr. 2015.

- [15] Specific Attenuation Model for Rain for use in Prediction Methods, Standard ITU-R P.838-3, 2005.

- [16] Fixed Radio Systems; Parameters Affecting Signal-to-Noise Ratio (SNR) Receiver Signal Level (RSL) Threshold Point-to-Point Receivers; Theory Practice, document ETSI TR 103 053 V1.1.1, 2014.

- D. del Rio et al., "A wideband millimeter-wave up-conversion mixer [17] for future backhaul E-band point-to-point links with a 0 dBm 1-dB compression point," in Proc. IEEE Int. Conf. Ubiquitous Wireless Broadband (ICUWB), Oct. 2015, pp. 1–5. [18] Characteristics of Precipitation for

- Propagation Modelling. for documnet ITU-R P.837-6, 2012.

- [19] A. Rezola et al., "Impact of AC coupling on zero-IF architectures for wide-band millimeter-wave gigabit transmitters," in Proc. 20th Eur. Wireless Conf., May 2014, pp. 1-6.

- [20] P. Chevalier et al., "A 55 nm triple gate oxide 9 metal layers SiGe BiCMOS technology featuring 320 GHz fT / 370 GHz fMAX HBT and high-Q millimeter-wave passives," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2014, pp. 3.9.1-3.9.3.

- [21] B. H. Ku, O. Inac, M. Chang, H. H. Yang, and G. M. Rebeiz, "A high-linearity 76-85-GHz 16-element 8-transmit/8-receive phased-array chip with high isolation and flip-chip packaging," IEEE Trans. Microw. Theory Techn., vol. 62, no. 10, pp. 2337-2356, Oct. 2014.

- [22] J.-H. Tsai, "Design of 40–108-GHz low-power and high-speed CMOS up-/down-conversion ring mixers for multistandard MMW radio applications," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 3, pp. 670–678, Mar. 2012.

- [23] C. E. Saavedra, D. del Rio, and R. Berenguer, "68–73 GHz commonbase HBT amplifier in 55 nm SiGe technology," in *Proc. Global Symp. Millim. Waves*, May 2015, pp. 1–3.

- [24] R. Yishay, R. Carmon, O. Katz, B. Sheinman, and D. Elad, "A 20 dBm E-band power amplifier in SiGe BiCMOS technology," in *Proc. 42nd Eur. Microw. Conf. (EuMC)*, Oct. 2012, pp. 1079–1082.

- [25] M. Thian, M. Tiebout, and V. F. Fusco, "Holistic design of 8-way combining transformers in SiGe technology for use in millimetrewave power amplifiers," in *Proc. IEEE 13th Topical Meeting Silicon Monolithic Integr. Circuits RF Syst. (SiRF)*, Jan. 2013, pp. 72–74.

- [26] B. Leite, E. Kerherve, J.-B. Begueret, and D. Belot, "Shielding structures for millimeter-wave integrated transformers," in *Proc. 16th IEEE Int. Conf. Electron., Circuits, Syst. (ICECS)*, Dec. 2009, pp. 239–242.

- [27] D. Chowdhury, P. Reynaert, and A. Niknejad, "Design considerations for 60 GHz transformer-coupled CMOS power amplifiers," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2733–2744, Oct. 2009.

- [28] T. Tired, H. Sjoland, C. Bryant, and M. Tormanen, "A 1 V SiGe power amplifier for 81–86 GHz E-band," in *Proc. NORCHIP*, Nov. 2013, pp. 1–4.

- [29] M. Rickelt, H.-M. Rein, and E. Rose, "Influence of impact-ionizationinduced instabilities on the maximum usable output voltage of Si-bipolar transistors," *IEEE Trans. Electron Devices*, vol. 48, no. 4, pp. 774–783, Apr. 2001.

- [30] C. M. Grens, "A comprehensive study of safe-operating-area, biasing constraints, and breakdown in advanced SiGe HBTs," Ph.D. dissertation, School Elect. Comput. Eng., Georgia Inst. Technol., Atlanta, GA, USA, Aug. 2005.

- [31] A. Rezola et al., "Frequency-selective IQ imbalance compensation in zero-second-IF transmitters for wide-band mmW links," Int. J. Commun., vol. 9, pp. 98–104, 2015.

- [32] S. Shahramian, Y. Baeyens, and Y.-K. Chen, "A 70-100 GHz directconversion transmitter and receiver phased array chipset in 0.18μm SiGe BiCMOS technology," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2012, pp. 123–126.

- [33] W.-H. Lin, H.-Y. Yang, J.-H. Tsai, T.-W. Huang, and H. Wang, "1024-QAM high image rejection *E*-band sub-harmonic IQ modulator and transmitter in 65-nm CMOS process," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 11, pp. 3974–3985, Nov. 2013.

- [34] J. Antes and I. Kallfass, "Performance estimation for broadband multi-gigabit millimeter- and sub-millimeter-wave wireless communication links," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 10, pp. 3288–3299, Oct. 2015.

- [35] M.-S. Kang, B.-S. Kim, K. S. Kim, W.-J. Byun, and H. C. Park, "16-QAM-based highly spectral-efficient E-band communication system with bit rate up to 10 Gbps," *ETRI J.*, vol. 34, no. 5, pp. 649–654, 2012.

- [36] J. Chen et al., "10 Gbps 16QAM transmission over a 70/80 GHz (E-band) radio test-bed," in Proc. 7th Eur. Microw. Integr. Circuits Conf. (EuMIC), Oct. 2012, pp. 556–559.

**Iñaki Gurutzeaga** was born in Hernani, Spain. He received the M.Sc. degree in telecommunication engineering from the Polytechnic University of Catalonia, Barcelona, Spain, in 1992, and the Ph.D. degree in the field of ultra-wideband devices for broadband communication systems at microwave frequencies from the TECNUN School of Engineering, University of Navarra, Navarra, Spain.

He possesses 18 years of experience as a Researcher and as the Product Manager in RF and microwave fields at three different companies:

FAGOR ELECTRONICA S. Coop., ALCAD S.A., and IKUSI S.A. Since 2003, he has been a Lecturer on devices and circuits of microwaves with TECNUN and a Research Scientist with the Sensor and Analog Electronics Group, ICT Division, Ceit-IK4, San Sebastian, Spain, in the area of integrated circuits design and antennas. He is involved in diverse projects in  $\mu$ W and millimeter-wave frequencies, up to sub-THz frequencies.

Ainhoa Rezola was born in San Sebastian, Spain, in 1990. She received the M.Sc. degree in telecommunication engineering from the Technology Campus of the University of Navarra, San Sebastian, in 2013. She is currently pursuing the Ph.D. degree at the Electronic and Communication Department, Ceit-IK4 Research Center, San Sebastian.

In 2013, she joined the Electronic and Communication Department, Ceit-IK4 Research Center. Her current research interests include digital signal processing and digital implementation.

Juan F. Sevillano (M'03) received the M.Sc. degree in electrical, electronic and control engineering and the Ph.D. degree from the University of Navarra, Navarra, Spain, in 1999 and 2004, respectively.

In 2000, he joined the Ceit-IK4 Research Center, San Sebastian, Spain, where he was involved in projects related to wireless communications and sensor systems. He is currently a Lecturer with the University of Navarra. His current research interests include signal processing and electronic systems implementation.

**Igone Velez** (M'06) received the M.Sc. degree in electrical, electronic and control engineering and Ph.D. degree from the University of Navarra, Navarra, Spain, in 2000 and 2005, respectively.

She has been a Research Staff Member with Ceit-IK4, San Sebastian, Spain, since 2000, and an Associate Professor with the University of Navarra since 2005. She is currently the Director of the ICT Division, Ceit-IK4. She has been involved in international and national projects related to UWB, RFID, and 5G technologies. Her current research

interests include design methodologies, signal processing, and hardware development for telecommunication systems.

Sten E. Gunnarsson (S'02–M'08) received the M.Sc. degree in electrical engineering from the Lund University of Technology, Lund, Sweden, in 2003, and the Ph.D. degree from the Chalmers University of Technology, Göteborg, Sweden, in 2008, respectively.

He was with Sivers IMA AB, Kista, Sweden, where he designed frequency converters and chipscale packages in the frequency range from 50 to 90 GHz. He was the Co-founder of GotMIC AB, a fabless and independent design house of

advanced MMIC solutions. He is currently a Research and Development Microwave Engineer with SAAB Technologies AB, Järfälla, Sweden. He is also a part-time employee with the Microwave Electronics Laboratory, Department of Microtechnology and Nanoscience, Chalmers University of Technology, where he is involved in supervision and research. He has authored or coauthored more than 50 peer-reviewed scientific papers. His current research interests include the design of MMICs and packaging solutions for wireless systems operating in the 50–340-GHz range.

Dr. Gunnarsson was a recipient of the IEEE Microwave Theory and Techniques Society Graduate Fellowship Award in 2006 and 2007.

**David del Rio** (GS'14) was born in San Sebastian, Spain, in 1990. He received the M.Sc. degree in telecommunication engineering from the TEC-NUN School of Engineering, University of Navarra, Navarra, Spain, in 2013.

He joined the Ceit-IK4 Communications IC Design Group, San Sebastian, Spain, as a Ph.D. student. In 2016, he was a Visiting Graduate Researcher with the High Speed Electronics Laboratory, University of California at Los Angeles, Los Angeles, CA, USA, where he was involved in the design of

integrated transceivers for 5G communications. His current research interests include millimeter-wave and RF circuit design, power amplifiers, and reconfigurable devices for self-healing systems.

Nataly Tamir received the B.Sc. degree in electrical engineering from Tel Aviv University, Tel Aviv, Israel, in 2004.

She was involved in the design and development of high power amplifiers in VHF/UHF/L/S bands as well as low power multifunctional modules in various bands up to the Ku-band. She is currently a Research and Development of Microwave Engineer with Sivers IMA AB, Kista, Sweden. She mainly focuses on E-band frequency converter design and high frequency PCB design.

Alexandre Siligaris was born in Greece, in 1977. He received the M.Sc. and Ph.D. degrees from the Science and Technology University of Lille, Villeneuve-d'Ascq, France, in 2001 and 2004, respectively. During his Ph.D. studies, he was involved in transistor characterization and modeling for high-frequency applications.

From 2004 to 2005, he was an Associate Professor with the Science and Technology University of Lille. In 2006, he joined CEA LETI, Grenoble, France. His work focuses on high-frequency modeling and

high-frequency circuit design in CMOS and BiCMOS advanced technologies.

Cédric Dehos joined CEA LETI, Grenoble, France, in 2003, after graduation in telecommunication and signal processing from ESIEE Paris, Noisy-le-Grand, France. Since then, he has been involved in system-level design of complex RF and digital circuits, including RF behavioral modeling, architecture design and specification, system simulation, and signal processing. His current research interests include UWB OFDM systems, digital compensation of RF imperfections, and antenna beamforming.

**Carlos E. Saavedra** (S'92–M'98–SM'05) received the Ph.D. degree from Cornell University, Ithaca, NY, USA.

From 1998 to 2000, he was a Senior Engineer with the Millitech Corporation. In 2000, he joined the Department of Electrical and Computer Engineering (ECE), Queen's University, Kingston, ON, Canada, where he is currently a Professor.

Prof. Saavedra was a three-time recipient of the third-year ECE Undergraduate Teaching Award of Queen's University. He is an Associate Editor of

the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, a member of the TPRC of the IEEE International Microwave Symposium (IMS), and a member of the IEEE NEWCAS Conference Steering Committee. He is a former Co-Chair of the Natural Sciences and Engineering Research Council of Canada Discovery Grants Evaluation Group 1510 and the Past Chair of the IEEE MTT-S Technical Coordinating Committee 22 on Signal Generation and Frequency Conversion. He served on the Steering and Technical Program Committees of the 2012 IEEE IMS and was a member of the IEEE RFIC Symposium TPC from 2008 to 2011.

Jose Luis Gonzalez-Jimenez (M'99-SM'12) received the Diploma in telecommunication engineering from Ramon Llull University, Barcelona, Spain, in 1992, the M.Sc. degree in telecommunications engineering and the Ph.D. degree (with Hons.) in electronic engineering from the Universitat Politecnica de Catalunya (UPC), Barcelona, in 1994 and 1998, respectively, and the Habilitation à Diriger des Recherches degree from Grenoble University, Grenoble, France, in 2013.

In 1999, he received a Fulbright Fellowship and was a Guest Researcher with the University of Arizona, Tucson, AZ, USA, where he collaborated with Motorola in the design of high-speed digital-to-analog converters. From 2007 to 2008, he was a Visiting Researcher with the STMicroelectronics/ CEA-LETI Joint Advanced Research Laboratory, Minatec, Grenoble, where he was involved in research on the design of millimeter-wave oscillators and substrate noise coupling in millimeter-wave CMOS integrated circuits. Until 2011, he was a Full-Time Associate Professor with the Department of Electronic Engineering, UPC. He is currently a Senior Expert and RFIC and Millimeter-Wave (mmW) Research Engineer with CEA/LETI. His current research interests include very large-scale integration design, mixed-signal/RF and mmW ICs, silicon photonics, and noise in system-on-chip and RFICs.

**Roc Berenguer** (M'05–SM'16) received the M.Sc. and Ph.D. degrees from TECNUN, Navarra, Spain, in 1996 and 2000, respectively.

From 1999 to 2015, he was with Ceit-IK4, San Sebastian, Spain, first as an Associate Researcher until 2013 and as the Head of the Electronics and Communication Unit until 2015. Through Ceit-IK4 and INCIDE (Spin-off of the Ceit's COMMIC group), he was an External Consultant with Siemens, Munich, Germany, in 2000, Hitachi Microsystems Europe, Maidenhead, U.K.,

in 2001, Xignal Technologies, Munich, from 2001 to 2002, Seiko-Epson, Barcelona, Spain, from 2006 to 2007, and Innophase, Chicago, IL, USA, from 2012 to 2014, where he collaborated in the design of several RF front-ends for wireless standards such as GSM-EDGE, DAB, and Wibree. He has transferred technology to two start-up companies: INCIDE S.A in 2000 (April 2014 INCIDE was acquired by IXYS and changed name to IXYS-San Sebastian) and FARSENS S.L in 2008. In 2009, he was a Visiting Researcher with the Illinois Institute of Technology (IIT), Chicago, where he was involved in the design of a 77-GHz receiver front-end in 65-nm CMOS for a FM-CW automotive radar. Since then, he has also been an Affiliated Researcher with the High Performance Integrated Circuits and Microsystems Laboratory, IIT. In 2010, he was a Visiting Scholar with the High Speed Electronics Laboratory, University of California Los Angeles (UCLA), Los Angeles, CA, USA, where he was involved in the design of a power amplifier at 60 GHz. He is currently an Associate Professor with the Electrical, Electronic and Control Engineering Department, Technological Campus of the University of Navarra, San Sebastian, Spain. He is also a Senior RFIC Design Engineer with Innophase Inc., San Diego, CA, USA. His current research interests include CMOS RF and millimeter-wave IC design, ultra-low power analog circuit design for batteryless sensor nodes, and high-speed signal processing. He has authored or co-authored over 70 refereed publications in journals and conferences. He holds ten patents and co-authored Design and Test of High Quality Integrated Inductors for RF Applications in Conventional Technologies (Springer, 2003), GPS and Galileo: Dual RF Front-End Receiver Design, Fabrication and Test (McGraw-Hill, 2008), and Linear CMOS RF Power Amplifiers (Springer, 2014). He is an advisor of the Spanish Agency of Evaluation and Prospective.

Dr. Berenguer served on the TPC of the IEEE European Solid State Circuit Conference, the IEEE Midwest Symposium Circuits and Systems, and the IEEE Ph.D. Research in Microelectronics and Electronics. He also served as a reviewer for several journals such as the IEEE JOURNAL OF SOLID-STATE CIRCUITS, IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECH-NIQUES, IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: REGULAR PAPERS, and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—II: EXPRESS BRIEFS.