# A Low-Power Low-Noise Decade-Bandwidth Switched Transconductor Mixer With AC-Coupled LO Buffers

Hao Li, *Member, IEEE*, Ahmed M. El-Gabaly, *Member, IEEE*, and Carlos E. Saavedra, *Senior Member, IEEE*

Abstract-In this paper, a modified switched transconductor mixer structure is proposed to realize a low-power, low-noise, and wideband mixer, in which, a transconductor stage with fixed dc operating point is switched by the ac-coupled local oscillator (LO) signal. In this way, only a small LO signal is required to turn the transconductor ON and OFF, and thus a low-power LO buffer can be used to achieve wideband down-conversion. To further expand the bandwidth, the inductive peaking technique is used at the RF port to eliminate the capacitive loading effect resulted from the input transistors. As the noise power from LO stage appears in common mode at the mixer output, good noise performance is realized, too. Additionally, output distortion-cancellation IF buffer is added to facilitate the testing. Fabricated in the 0.13- $\mu m$  CMOS process, 15.5–17.5-dB gain and 4–5.2-dB noise figure are achieved in 1-10-GHz bandwidth. The mixer core consumes a low power of 8.3 mW from 1.5-V supply, and the whole chip consumes 22.3 mW, including the IF buffer. The active chip area is less than 0.2 mm<sup>2</sup>.

*Index Terms*—Low power, low noise, switched transconductor mixer, ultra-wide band (UWB), mixer.

# I. INTRODUCTION

**R**OBUST demand for multi-band wireless handheld devices and infrastructure continues to drive research in broadband RF front-end (RFE) techniques. As the number of communication bands increases to provide more functionality, to handle more users and to enable higher speeds, the bandwidth, noise figure (NF) and linearity specifications of wideband receivers are becoming more stringent. Ultra broadband active down-conversion mixers are attractive for multi-band RF receivers because they have the known benefits of high gain and low local oscillator (LO) power, yet their moderate to high NF levels, in the absence of noise mitigation strategies,

Manuscript received March 4, 2017; revised June 12, 2017 and July 16, 2017; accepted August 1, 2017. Date of publication August 16, 2017; date of current version January 25, 2018. This work was supported by a grant from the Natural Sciences and Engineering Research Council of Canada. This paper was recommended by Associate Editor Y. Sun. (*Corresponding author: Hao Li.*)

H. Li and C. E. Saavedra are with the Department of Electrical and Computer Engineering, Queen's University, Kingston, ON K7L 3N6, Canada (e-mail: h.li@queensu.ca; saavedra@queensu.ca).

A. M. El-Gabaly was with Queen's University, Kingston, ON K7L 3N6, Canada. He is now with Broadcom Corporation, Irvine, CA 92617 USA (e-mail: ahmed.el-gabaly@broadcom.com).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2017.2736439

places strict gain and NF requirements on the preceding lownoise amplifier (LNA). Therefore, further advances are needed in ultra broadband low-noise mixers to relax such requirements on the LNA without compromising interdependent performance metrics, including power dissipation.

Several different topologies exist for wideband low-noise down-conversion [1]–[5]. Among them the most recent and effective approaches are based on current-commutating mixers with noise-cancelling transconductors [1]–[3]. The noise cancellation can be realized in various forms. A cross-coupled transistor pair is used in [1] to realize partial noise cancellation of the common-gate input transistors. A parallel common-source transistor is employed in [2] and [3] to cancel the noise of the common-gate input transistors.

Often, the mixer LO switches are implemented at the current mirror nodes of an amplifier in [4] to achieve wideband low-noise down-conversion. While this technique combines the advantages of passive and active mixers, such as low noise and high gain, its noise bandwidth is limited due to the use of a resonating tank to suppress the major noise contributors. In [5], the bulk-injection technique is adopted to realize a mixer that covers the span 3.1-10.6 GHz at a low power consumption of 0.88 mW but a NF of 11.7 dB.

In addition to the efforts in wideband low-noise downconversion described above, the switched transconductor mixer (STM) proposed in [6] shows superior noise performance with low power consumption and low voltage supply. With the transconductors turned on and off by the switches connected to the supply rails, this mixer's NF is lower compared to its current-commutating counterpart for high LO frequencies due to the absence of LO noise at the output. One method to expand the bandwidth of the STM topology is by adding a push-pull LO driver [7], yet this approach increases the power dissipation of the circuit.

In this paper, a modified STM structure is proposed to realize a low-power, low-noise, ultra broadband mixer, in which a transconductor stage with fixed DC operating point is switched by the ac-coupled LO signal. In this way, only a small LO signal is required to turn the transconductor on and off and thus a low-power LO buffer can be used to achieve wideband down-conversion. As the noise power from LO stage appears in common mode at the mixer output, a low NF performance is achieved. Besides the mixing core, inductive peaking is used

1549-8328 © 2017 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

at the RF port to eliminate the capacitive loading effect from the input transistors. To facilitate experimental testing of the mixer, an IF buffer is also integrated on-chip to drive the output 50- $\Omega$  load. The buffer incorporates a derivative superposition distortion canceling (DS) subcircuit [8]–[11] to reduce the intermodulation distortion it produces to better characterize the mixer's IP<sub>3</sub> performance.

Here, we go beyond the work reported in our recent paper [12] and provide more in-depth analysis. In Section II, the bandwidth analysis for both the baseline and proposed switched transconductor mixers are conducted. Besides, the design process of the proposed mixer is described in details with the performance comparison to its baseline counterpart provided. In Section III, IC implementation details are described including a NF analysis to provide necessary insight into the main noise contributors and verifies the effectiveness of series inductive peaking. Section IV provides the measurement results of the chip and the conclusions are drawn in Section V.

# II. PROPOSED METHOD TO INCREASE THE BANDWIDTH OF THE STM

A qualitative description of the factors that impact the frequency response of the baseline STM is first provided followed by the proposed method to improve the bandwidth of the STM using a modified STM (MSTM). A detailed one-to-one comparison between the baseline STM and the MSTM is carried out in simulation to show the effectiveness of the new approach.

# A. Bandwidth Considerations in the Baseline STM

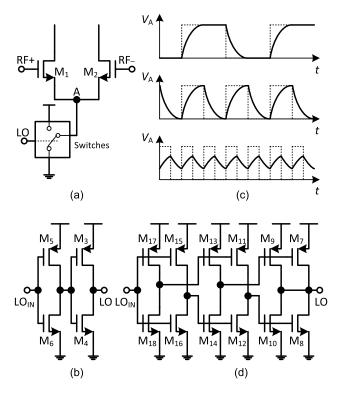

The circuit diagram of the baseline STM topology is given in Fig. 1(a). It uses a differential pair ( $M_1$ ,  $M_2$ ) as the transconductor and a switching block [6]. The switch is driven by the LO signal and turns the transconductor pair on and off by chopping its tail current, thus producing the mixing action. The topology is very well-suited for low-voltage applications and demonstrates potential for significant reductions in NF, because the noise from the LO stage appears in common mode at the mixer output and thus does not deteriorate the differential output signal.

Similar to the current-commutating mixer, the STM transconductor needs to be turned completely on and off with little transition time to achieve best performance. This is achieved by the switching stage, which is typically built with CMOS inverters. In a fully-integrated radio chip, the LO power produced by the frequency synthesizer requires an additional boost to produce a suitable waveform to drive the mixer such as the inverter chain depicted in Fig. 1(b). At low LO frequencies, with proper transistor dimensions chosen for the LO buffers and the switch,  $V_A$  can be switched between supply rail and ground completely and symmetrically. As a result, the conversion gain of the STM is verified [6] to be the same as that of the current-commutating mixer.

A salient factor that impacts the bandwidth of the STM is the ability of the LO switches and the inverter-based buffers to produce a rail-to-rail output as the frequency increases. As

Fig. 1. Bandwidth study of the baseline STM: (a) schematic of the baseline STM [6]; (b) schematic of the inverter-based LO buffer [6]; (c) waveform of  $V_A$  with the increase of LO frequency; (d) schematic of the "push-pull" LO buffer [7].

illustrated in Fig. 1(c), as the LO frequency increases, the time that can be used for the high/low transitions of  $V_A$  decreases while the time constants of the inverters remain unchanged. Eventually when the frequency is larger than a certain value,  $V_A$  cannot fully transition from rail to rail. Transients will make the sawtooth waveform  $V_A$  drift up and down from the center, which compromises the on/off switching response of the transconductor and, hence, the mixer.

Efforts have been made to expand the bandwidth of the STM by adding a wideband LO driver. One such driver used in [7] is drawn in Fig. 1(d), which is a "push-pull" structure to increase the output current-driving behavior. Furthermore, the common-mode voltage of the driver's output is fixed by the common-mode feedback circuit. In this way, even if the magnitude of the driver output voltage cannot reach the supply rail at high frequency, the transient drift of the signal at  $V_A$ is much reduced. With  $V_A$  more consistently centered at the middle of the supply voltage, the transconductor's switching is sustained up to a higher frequency than before. The cost of increasing the frequency response with the push-pull driver in Fig. 1(d) is a noticeable increase in the power consumption. For instance, to obtain an STM with 8 GHz bandwidth, the buffer design in [7] draws 5 mA per LO+/LO- buffer from a 1.2 V supply.

# B. The Proposed MSTM Concept

Based on the above analysis, STM is power-consuming when operating in wideband because the switches require wideband LO drivers, which dissipate large amount of power. Addressing this issue, a modified STM (MSTM) is proposed,

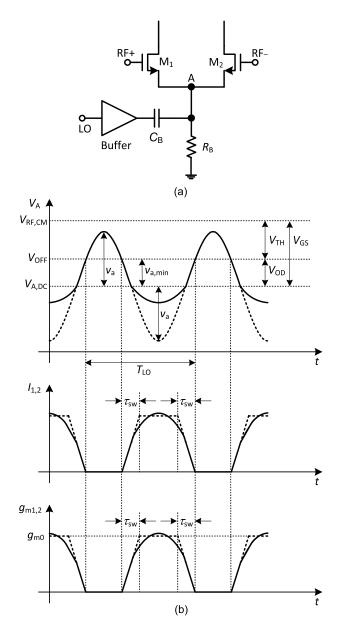

Fig. 2. Bandwidth analysis of the modified STM (MSTM) (a) schematic of the MSTM; (b) waveforms of  $V_A$ , current through the transconductors  $I_{1,2}$  and their transconductance  $g_{m1,2}$ .

in which transconductors can be turned on and off without railto-rail-operating switches, and the power-hungry LO drivers of the switches can be eliminated while an ultra-wide band can still be achieved. In this way, the power consumption can be decreased with the same LO power as STM.

The proposed MSTM is depicted in Fig. 2(a). The transconductor stage consists of the differential pair ( $M_{1-2}$ ) and a resistor  $R_B$ . The LO signal is fed-in through the coupling capacitor  $C_B$  to turn the transconductor on and off and an LO buffer amplifier provides the driving ability. In the following, the working principle of the MSTM is described to show how a nearly-constant conversion gain over an ultrabroad bandwidth is achieved when the LO signal power exceeds a small threshold while keep the buffer circuit power consumption at a low level. If the LO signal reaching node A in Fig. 2(a) is small, the circuit forms a multiplier because RF and LO signals together modulate the transconductance  $(g_m)$  of M<sub>1,2</sub>. In this case, the conversion gain exhibits a quite linear dependence on the strength of the LO signal. As the LO power increases, M<sub>1,2</sub> will turn off for part of the LO period. As the LO keeps rising, M<sub>1,2</sub> can eventually turn off for approximately half of the period. Consequently, the transconductor is turned on and off alternately by the LO and a mixer with similar behavior of STM is realized.

Next, two key points related to the working principle of the MSTM will be discussed: (i) the minimum voltage swing of  $V_A$  needed to fully turn the transconductor off and (ii) the effective  $g_m$  of the MSTM. To assist the explanation, refer to Fig. 2(b) which shows the waveform at node A, the currents  $I_{1,2}$  through M<sub>1,2</sub>, and the instantaneous transconductance of the transistors  $g_{m1,2}$ .

The transconductor has to be biased at a point where  $M_{1,2}$  can provide substantial transconductance. As seen in Fig. 2(b), the bias voltage of the gates and the sources of  $M_{1,2}$  are denoted as  $V_{\text{RF,CM}}$  and  $V_{\text{A,DC}}$ , respectively. In this way, the overdrive voltage of  $M_{1,2}$ ,  $V_{\text{OD}}$ , is

$$V_{\rm OD} = V_{\rm RF,CM} - V_{\rm A,DC} - V_{\rm TH} \tag{1}$$

in which  $V_{\text{TH}}$  represents the threshold voltage of M<sub>1.2</sub>. Under this condition, the transconductance of  $M_{1,2}$  is denoted as  $g_{m,0}$ , and the impedance looking into the node A from the buffer output is  $(1/2g_{m,0})//R_B$ . Second, in the MSTM, the load of the LO buffer varies as a function of the transconductance of  $M_{1-2}$ , which impacts  $V_A$ . For the trivial case when the LO buffer drives a fixed impedance equal to the impedance of node A under DC bias, i.e. $(1/2g_{m,0})//R_B$ , let the amplitude of the buffer output be denoted as  $v_a$ , as illustrated with the dashed curve in Fig. 2(b). Now, the solid curve in Fig. 2(b),  $V_A$  is in fact asymmetrical to  $V_{A,DC}$ . As  $V_A$  increases, the output impedance of the buffer increases from  $(1/2g_{m,0})//R_B$  towards  $R_{\rm B}$ , which reinforces the rise of  $V_{\rm A}$ . As a result, the upper half increment of  $V_A$  from  $V_{A,DC}$  is somewhat larger than  $v_a$ . For simplicity, let it be equal to  $v_a$ . The smallest value of  $V_A$  that turns  $M_{1,2}$  off, denoted as  $V_{OFF}$ , is

$$V_{\rm OFF} = V_{\rm RF,CM} - V_{\rm TH},\tag{2}$$

the corresponding minimum amplitude of the buffer output needed to turn off  $M_{1,2}$  can be written as

$$v_{a,\min} = V_{OD}.$$

(3)

When  $v_a$  increases beyond  $v_{a,\min}$ , the transconductor will remain off.

On the other hand, with the same amplitude fed into the LO buffer, the low voltage appearing at the buffer output, denoted as  $V_{ON}$ , is much closer to  $V_{A,DC}$  due to the negative feedback in the system. As  $V_A$  decreases, the transconductance of  $M_{1,2}$  increases, which decreases the load impedance and thus the gain of the buffer. Therefore, the drop in  $V_A$  is diminished and  $V_A$  still remains close to  $V_{A,DC}$ . Thus with a large range of  $v_a$ , the effective transconductance of the MSTM is approximately  $g_{m,0}$ , which is the transconductance under the DC bias as described above.

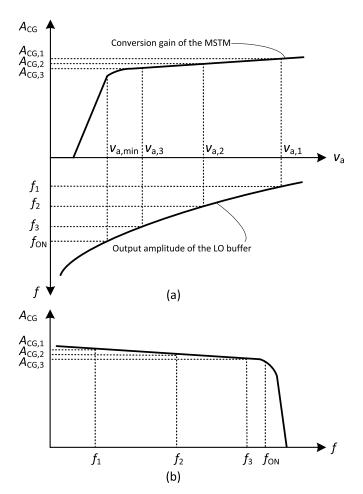

Fig. 3. Frequency response of the modified STM (a) with  $V_A$  as an intermediate variable; (b) direct relation between conversion gain and frequency.

To summarize,  $v_a$  must exceed  $v_{a,min}$  given by (3) to make the MSTM work properly. When  $v_a$  is small, the conversion gain increases linearly to  $v_a$ . As  $v_a$  exceeds  $v_{a,min}$ , the effective transconductance remains close to  $g_{m,0}$  and thus the conversion gain stays as a constant as  $v_a$  increases. The relation between the conversion gain and  $v_a$  is further illustrated by the curve in Fig. 3(a). As can be seen, when  $v_a$  is smaller than  $v_{a,min}$ , the conversion gain increases linearly. As  $v_a$  exceeds  $v_{a,min}$ , the conversion gain tends to stay stable. This character is used here to make the MSTM operate in a wide band without having a power-consuming wideband LO driver, as explained below.

For the low-pass LO buffer with a certain bandwidth, its output power rolls off quickly at high frequencies, as illustrated in Fig. 3(a). With the increase of LO frequency from  $f_1$  to  $f_3$ , the amplitude at the buffer output drops considerably from  $v_{a,1}$  to  $v_{a,3}$ . However, as  $v_{a,1}$ ,  $v_{a,2}$  and  $v_{a,3}$  are all larger than  $v_{a,min}$ , the conversion gain realized by MSTM,  $A_{CG,1} - A_{CG,3}$ , are close to one another. Consequently, a nearly flat conversion gain of the MSTM over a wide frequency from  $f_1$  to  $f_3$  is achieved, which is illustrated in Fig. 3(b). Therefore, with this feature, a very low-power LO buffer can be used to realize wide-band down-conversion.

## C. Simulation Verification

A double-balanced mixer based on the proposed MSTM topology is designed in a standard 0.13  $\mu$ m CMOS process.

Design process and the related simulation results are demonstrated in details. Additionally, an STM design instance is provided for comparison purposes.

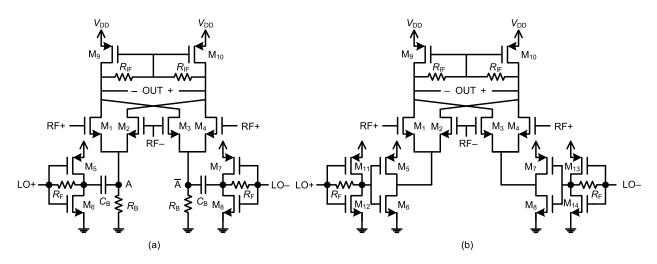

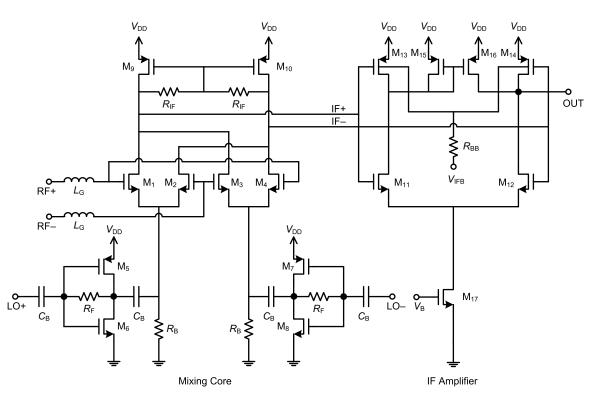

1) Wideband MSTM Design: The schematic of the doublebalanced MSTM is shown in Fig. 4(a).  $M_{1-4}$ ,  $R_B$  and  $C_B$  are used to realize the MSTM core proposed in Section II-B. Complementary, current-reused amplifiers ( $M_{5-8}$ ,  $R_F$ ) are adopted to realize the LO driver which is symbolized in Fig. 2(a). Additionally, self-biased current sources ( $M_{9-10}$ ,  $R_{IF}$ ) are used to provide a high-impedance load of the mixer.

In this design, the width of  $M_{1-4}$  is made relatively large ( $W = 80 \ \mu m$ ) so that  $V_{GS}$  is close to the threshold voltage  $V_{TH}$ . This arrangement is made so that a large transconductance can be obtained when the transconductor is turned on, and low input-referred noise can thus be achieved. Second, a very low overdrive voltage near 0 V results in this way, which allows the transconductor to turn off easily.

The LO buffers adopt the current reuse complementary amplifier structure for its high current efficiency to generate transconductance  $(g_m)$ , as seen from Fig. 4(a).  $R_F$  is used to stabilize the output DC voltage while its resistance is chosen to be large enough to realize adequate gain of the amplifier. The transfer function of the amplifier can be approximately expressed as  $(g_{mN} + g_{mP})(r_{0N}//r_{0P}//R_A//C_A)$ , in which  $R_A$ and  $C_A$  represent the resistance and capacitance at node A and the rest represent their usual meanings for the LO buffer. As described in foregoing analysis,  $R_A$  equals to  $(1/2g_{m,0})//R_B$ under DC bias point, which is close to 50  $\Omega$  in this design. With 1.5 mA current assigned to each single-ended LO buffer, a -0.5 dB gain with 3-dB bandwidth of 10 GHz is achieved.

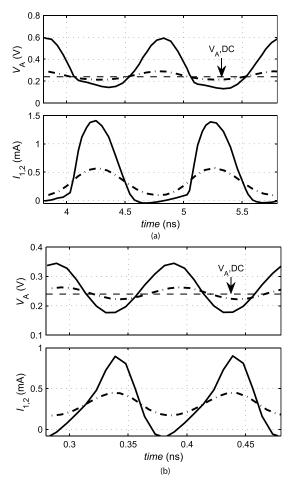

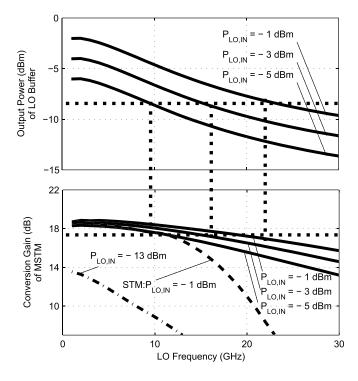

Simulation waveforms of the common source voltage  $V_A$ and current through  $M_{1,2}$  noted as  $I_{1,2}$  are plotted in Fig. 5. The waveforms of both 1 GHz and 10 GHz when the LO power is -1 dBm are plotted (solid line). As can be observed, when the LO frequency is 1 GHz, the transistor is off when  $V_{\rm A}$  exceeds around 0.3 V and on otherwise. The shape of waveforms for both voltage and current are same as predicted in Fig. 2(b). With the frequency increasing to 10 GHz, the magnitude of  $V_{\rm A}$  decreases due to the limited bandwidth of the LO driver. As a consequence, the duty cycle within which  $M_{1,2}$  are fully on or off decreases and the transition time increases correspondingly. What is more, due to the decrease of the  $V_A$  magnitude, the maximum current when  $M_{1,2}$  are on decreases to around 0.8 mA, which leads to a decrease of the effective  $g_{\rm m}$  of the mixer. The increase of the transition time and decrease of the effective  $g_m$  from 1 GHz to 10 GHz are the two causes for the conversion gain drop. However, as depicted by the conversion gain curve in Fig. 6, the gain drop is around 2 dB from 1 GHz to 10 GHz when the LO power is -1 dBm. In this manner, a wideband operation is achieved.

For comparison, the waveforms for both 1 GHz and 10 GHz when the LO power is 12 dB smaller (-13 dBm) are plotted in Fig. 5 (dashed line), too. Under this condition, even at 1 GHz,  $V_A$  magnitude is too small to fully turn  $M_{1,2}$  off. As a result, the LO signal is modulating  $g_m$  and the conversion gain is approximately linear to the signal strength of LO buffer output, as mentioned in the preceding description. To verify

Fig. 4. (a) Double-balanced modified switched transconductor mixer (MSTM). (b) Double-balanced switched transconductor mixer (STM) with current-reuse amplifiers as LO buffers.

it, the conversion gain curve when LO power is -13 dBm is also plotted (dashed line) in Fig 6. As can be seen, the gain drop is around 5 dB from 1 GHz to 10 GHz, and the slope of the curve is approximately the same as the LO buffer output, which is depicted in the upper plot in Fig 6. Besides the much smaller bandwidth, the conversion gain is smaller because a lower effective  $g_m$  is produced.

The LO input power also affects the bandwidth of the mixer. To reveal this relation, the voltage conversion gain of the MSTM and the output power of the LO buffer at node A are drawn with different input LO power levels in Fig 6. As before, the impedance of node A changes with  $V_A$ . To obtain a normalized output power of the LO buffer over frequency, assume that the buffer is driving a fixed load of  $(1/2g_{m,0})//R_B$ . From the graphs, it is easily observed that the rolloff of the conversion gain is much slower than that of the LO buffer output power for the LO input power is -5 dBm and above. Thus, wider bandwidth can be obtained for the MSTM than that of the adopted LO buffer. When an LO power of -5 dBm is fed-in, the voltage conversion gain of the mixer drops by 1 dB at about 10 GHz from its low frequency value, while the corresponding LO output power is around -8 dBm at 10 GHz. When the input LO power increases to -1 dBm, under the same LO buffer bandwidth, the frequency at which the LO output power drops to -8 dBm is widened to around 23 GHz. Correspondingly, the -1 dB bandwidth of the voltage conversion gain is extended to about the same frequency of 23 GHz, as expected. In this work, the input LO power of -1 dBm is adopted to achieve a flatter conversion gain.

The design parameters and the performances are summarized in Table I and II, respectively.

2) Performance Comparison With STM: To demonstrate the power efficiency of the proposed MSTM, an STM is designed with the same 0.13  $\mu$ m process to achieve the same bandwidth for comparison purposes. For a fair comparison, the same supply voltage of 1.5 V, notwithstanding the fact that the STM can work at lower supply voltages. The resistor  $R_{\rm B}$  in the MSTM inevitably reduces its voltage headroom, which

Fig. 5. Waveforms of  $V_A$  and  $I_{1,2}$  with LO input power at -1 dBm (solid line) and -13 dBm (dashed line) when LO frequency is (a) 1 GHz, (b) 10 GHz.

precludes its use in low-voltage environments—a conscious design trade-off in order to improve energy efficiency. The same LO power is adopted for the two mixers and the components sizes are chosen to be equal whenever possible, as summarized in Table I.

The schematic of the STM is shown in Fig. 4(b). With an input LO of -1 dBm, buffers are needed to properly drive the

| Property           |                      | MSTM                  |              | STM                  |                        |              |  |

|--------------------|----------------------|-----------------------|--------------|----------------------|------------------------|--------------|--|

| . ,                |                      |                       |              | 511/0                |                        |              |  |

| $g_{\sf m}$ & Load | (W/L) $_{1-4}$       | (W/L) <sub>9,10</sub> | $R_{IF}$     | (W/L) $_{1-4}$       | (W/L) <sub>9,10</sub>  | $R_{IF}$     |  |

| Devices            | 80/0.12              | 130/0.4               | 3 k $\Omega$ | 80/0.12              | 130/0.4                | 3 k $\Omega$ |  |

| Switching          | (W/L) <sub>5,7</sub> | (W/L) <sub>6,8</sub>  |              | (W/L) <sub>5,7</sub> | (W/L) <sub>6,8</sub>   |              |  |

| &                  | 45/0.12              | 15/0.12               |              | 30/0.12              | 15/0.12                |              |  |

| Driving            | $R_{B}$              | $R_{F}$               | $C_{B}$      | (W/L) 11,13          | (W/L) <sub>12,14</sub> | $R_{F}$      |  |

| Devices            | 400 Ω                | 3 kΩ                  | 4 pF         | 90/0.12              | 28/0.12                | 150 Ω        |  |

| Simulation         | Voltage              | LO                    |              | Voltage              | LO                     |              |  |

| Parameters         | 1.5 V                | - 1 dBm               |              | 1.5 V                | - 1 dBm                |              |  |

TABLE I

Overview of the Simulation Parameters Used for STM and MSTM Mixers of Fig. 4

Fig. 6. Output power of LO buffer and voltage conversion gain of the MSTM.

switches up to 10 GHz. In the 0.13  $\mu$ m process used here, the time constant of the inverter is around 20 ps when driving the inverter of the same size. Therefore, a simple inverter is not a suitable choice to implement the buffer. Instead, a current-reuse complementary amplifier is adopted for design simplicity, as seen in Fig. 4(b). With the bandwidth of STM guaranteed to be the same as the MSTM, the sizes of the switches (M<sub>5-8</sub>) and the drivers (M<sub>9-12</sub>) are optimized for the least power consumption.

The performances of the two mixers at 1, 4, 7 and 10 GHz are summarized in Table II. As well, the conversion gain curve over LO frequency of the STM is also drawn in Fig. 6 for comparison purpose. From the conversion gain variation over LO frequencies, it is found that from 1 to 10 GHz, the gain drops for the two mixers are approximately the same. When the LO frequency is beyond 10 GHz, the gain of STM drops drastically because of the failure of the switches.

As can be observed from Table II, with the same transistor sizes for the transconductors and the load, the two mixers demonstrate conversion gain and noise figure of the same level in the operating band from 1 to 10 GHz. Because of the modulating effects of the  $g_m$  by the LO when the transconductors are on, the IIP<sub>3</sub> of the MSTM is 2–4 dB worse than that of the STM. What is more, the simulated IIP<sub>2</sub> with IF frequency of 250 MHz and two-tone spacing of 10 MHz is also provided in Table II. Although a degradation is observed compared to the STM, the IIP<sub>2</sub> of the MSTM is still acceptable for the linear receiver. In wideband systems, for often times the intermodulation products fall into RF band of interest before the downconversion, which causes a severe deterioration of the IIP<sub>2</sub>. If possible, band-select filter can be adopted at the front-end to mitigate the IIP<sub>2</sub> requirements.

The power consumption of the MSTM is 8.25 mW, which consists of 3.75 mW for the transconductance core and 4.5 mW for the LO buffer. The power consumption of the STM also consists two parts, one for the mixer itself and the other for the LO driver. The mixer itself consumes a static power of 3.75 mW for the transconductor and a dynamic power for the switches, ranging from 0.78 mW at 1 GHz to 7.84 mW at 10 GHz (around 0.78 mW/GHz). The LO driver for the STM consumes a power of 9 mW.

If the STM is designed for a narrower bandwidth, the power-hungry LO driver can be substituted with a much power-efficient inverter. What is more, the sizes of the switches  $(M_{5-8})$  can also be decreased, so that even less dynamic power is consumed. In such a manner, the STM is more power-efficient than the proposed MSTM. However, for the STM to reach a bandwidth of 10 GHz requires 20.59 mW of total dc power, which is 2.5 times more power than the MSTM needs to yield the same bandwidth.

From this performance comparison, it can be concluded that the MSTM renders competitive performance compared to traditional STM when both are designed for wideband operation with the same LO power. The MSTM is more powerefficient at the cost of the reduced voltage headroom as well as the degraded IIP<sub>3</sub>.

# **III. IC IMPLEMENTATION**

A mixer RFIC using the proposed MSTM is designed and fabricated in a standard 0.13  $\mu$ m CMOS process and its schematic is provided in Fig. 7. The mixer core adopts

TABLE II Simulated Performance of the STM and MSTM Mixers of Fig. 4 for a Fixed IF = 250 MHz

|                                             | MSTM |      |      |      | STM   |       |       |       |

|---------------------------------------------|------|------|------|------|-------|-------|-------|-------|

| LO Frequency (GHz)                          | 1    | 4    | 7    | 10   | 1     | 4     | 7     | 10    |

| Conversion Gain (dB)                        | 19.6 | 19.5 | 18.8 | 17.8 | 19.7  | 19.4  | 17.9  | 16.6  |

| NF (dB)                                     | 4.3  | 4.4  | 4.7  | 5.4  | 4.4   | 4.8   | 5.9   | 6.9   |

| IIP <sub>3</sub> (dBm)                      | -0.6 | -2.6 | -1.2 | -1.1 | 4.3   | 3.2   | 2.5   | 1.7   |

| IIP <sub>2</sub> (dBm)                      | 42.0 | 38.6 | 39.1 | 39.6 | 49.7  | 42.5  | 40.0  | 55.0  |

| P <sub>dis</sub> MSTM / Static for STM (mW) | 3.75 | 3.75 | 3.75 | 3.75 | 3.75  | 3.75  | 3.75  | 3.75  |

| P <sub>dis</sub> dynamic for STM (mW)       | -    | -    | -    | -    | 0.78  | 3.14  | 5.49  | 7.84  |

| P <sub>dis</sub> LO Buffer (mW)             | 4.5  | 4.5  | 4.5  | 4.5  | 9     | 9     | 9     | 9     |

| P <sub>dis</sub> Total (mW)                 | 8.25 | 8.25 | 8.25 | 8.25 | 13.53 | 15.89 | 18.24 | 20.59 |

Fig. 7. Circuit schematic of the proposed mixer.

the same topology and design parameters used in the simulations in the previous section. Besides, two modifications are made for the convenience of the testing as well as better performance. First, inductors ( $L_G$ ) are added at the gate of transconductor transistors to compensate the gain and noise degradation in high frequencies caused by input parasitic capacitors. Second, an IF output buffer is designed to convert the differential output to single-ended and to provide the 50-ohm output impedance, which simplifies the testing. Distortion-cancelling technique is used in the IF buffer to eliminate its non-linear effect to the mixer. The design details and modelling of the chip are provided in this section.

# A. Input Inductive Peaking

Although a flat voltage gain over a wide band is obtained, the mixer could still hardly achieve wideband because of the pole introduced by the input capacitors of the mixer. As in foregoing description, the width of  $M_{1-4}$  is made relatively large for the best of the performance. However, larger device width implies higher gate parasitic capacitances (dominated by  $C_{GS}$ ), which introduces substantial loading effect to the preceding stage and deteriorates the gain and NF.

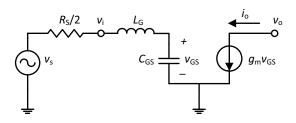

To further enhance the performance at high frequency, inductors  $L_G$  are added in series with the gates of  $M_{1-4}$ , as shown in Fig. 7.  $L_G$  can mitigate the loading effect through forming an inductive peaking network to delay the charging of the gate capacitors by the preceding stage. In a single-chip receiver,  $L_G$  is typically used together with the load inductor of the preceding stage to form shunt-and-series or shuntand-double-series peaking [13] to trade the delay for the bandwidth. While in this work, as the proposed mixer is designed as a stand-alone chip for research purposes,  $L_G$  is

Fig. 8. Small signal half-circuit model of  $M_{1-4}$  with  $L_G$  under test.

adopted here to prevent  $C_{\text{GS}}$  from loading the signal source in the testing.

The small signal half-circuit of the transconductor stage is given in Fig. 8. As can be seen, in the absence of  $L_{\rm G}$ , the source impedance  $R_S/2$  and  $C_{GS}$  form a low-pass network, which degrades its performance at high frequency. With  $L_{\rm G}$ added,  $R_S/2$ ,  $C_{GS}$  and  $L_G$  form a series inductive peaking network. The value of  $L_{G}$  is chosen based on tradeoffs between the maximum bandwidth, the maximum flatness and minimum phase distortion [14]. For a stand-alone chip,  $L_{\rm G}$ value that fulfills  $R_{\rm S}/2 = \sqrt{L_{\rm G}}/\sqrt{C_{\rm GS}}$  is preferred. In this way,  $L_{G}$  and  $C_{GS}$  form an "L" model of transmission line with characteristic impedance of  $R_S/2$ , which can be regarded as an "extension" of the source impedance all the way to the gate of the input transistors. Through the parasitic extraction, it is found that the  $C_{GS}$  is around 125 fF, so 0.31 nH should be chosen for  $L_G$ . In this work, a larger inductor of 0.5 nH is adopted, so that the small gain drop due to the LO power drop at high frequency can be compensated, too.

## B. Quantitative Analysis and Simulation Results

According to [6], the conversion gain expression of the switched transconductance mixer is the same as current steering mixer. With the input network taken into consideration, the conversion gain of the proposed mixer under test can be expressed as

$$A_{\rm CG,V} = \frac{c_0 g_{\rm m,0} R_{\rm O}}{\sqrt{(1 - \omega^2 L_{\rm G} C_{\rm GS})^2 + \omega^2 (R_{\rm S}/2)^2 C_{\rm GS}^2}}$$

(4)

where  $R_0$  is the load resistance.  $c_0$  represents the nominal value of the voltage conversion gain for the switching operation alone, and is equal to  $2/\pi$  if the transition time is short enough to be ignored [6], [15].

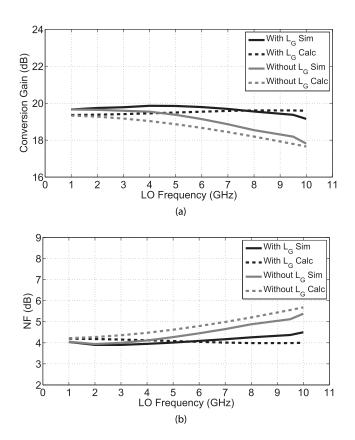

The calculated and simulated conversion gain curves with and without  $L_G$  are shown in Fig. 9(a). A good matching can be observed between the two, yet there is still some deviation. This is because,  $g_{m,0}$ , which is used in the calculation, is slightly different from the actual effective transconductance. In this way, the trivial rolling-off of the conversion gain caused by the LO drop, as depicted in Fig. 2(b), is not considered in the calculation. Nevertheless, the calculated result can well describe the trend of the gain change and the error is of limited amount.

The simulation result shows that a high gain of 19.5 dB is achieved and only around 1 dB drop is observed at 10 GHz with  $L_G$  added. Comparing the curves of conversion gain with

Fig. 9. Simulated gain and NF of the mixer core with and without  $L_{G}$ .

and without  $L_G$ , it can be observed that the gain at 10 GHz can be pulled up by around 1.5 dB.

The NF of switched transconductor mixers was analyzed before in [6], and the analysis is analogous to that of Gilbert cell mixers [15]. Here we analyze the NF of this mixer using the same approach [6], [15], but with  $L_{\rm G}$  and  $C_{\rm GS}$  taken into account to capture the frequency response. The thermal noise  $(S_{\rm n})$  at the output of the mixer (IF+ and IF- in Fig.7) is given by:

$$S_{\rm n} = \alpha 4kT R_{\rm S} \frac{g_{\rm m}^2}{\left[ \left( 1 - \omega^2 L_{\rm G} C_{\rm GS} \right)^2 + \omega^2 (R_{\rm S}/2)^2 C_{\rm GS}^2 \right]} + \alpha 4kT (2\gamma g_{\rm m}) + \alpha 4kT (2\gamma g_{\rm mp}) \,.$$

(5)

A portion of which is due to the input source resistance:

$$S_{\rm sn} = 4kTR_{\rm S} \frac{2c_0^2 g_{\rm m}^2}{\left[ \left( 1 - \omega^2 L_{\rm G} C_{\rm GS} \right)^2 + \omega^2 (R_{\rm S}/2)^2 C_{\rm GS}^2 \right]}.$$

(6)

So the double sideband (DSB) noise factor (F) is given by:

$$F = \frac{S_{\rm n}}{S_{\rm sn}} = \frac{\alpha}{2c_0^2} + \frac{\alpha}{2c_0^2} \frac{2r_{\rm g}}{R_{\rm S}} + \frac{\alpha}{2c_0^2} \frac{2\gamma}{g_{\rm m}R_{\rm S}} \left[ \left( 1 - \omega^2 L_{\rm G}C_{\rm GS} \right)^2 + \omega^2 \left( R_{\rm S}/2 \right)^2 C_{\rm GS}^2 \right] + \frac{\alpha}{2c_0^2} \frac{2\gamma g_{\rm mp}}{g_{\rm m}^2 R_{\rm S}} \left[ \left( 1 - \omega^2 L_{\rm G}C_{\rm GS} \right)^2 + \omega^2 \left( R_{\rm S}/2 \right)^2 C_{\rm GS}^2 \right]$$

(7)

where  $g_{\rm mp}$  is the transconductance of  $M_9 - M_{10}$ .  $\gamma$  is the excess noise factor and chosen to be 1.33 for the calculation.

$\alpha$  models the effective noise folding due to switching. It is equal to the power of the (normalized) switched transconductance waveform, which varies between +1 and -1 as the RF transconductors alternately turn on and the output current is commutated. 0.4 is chosen for  $\alpha$  here, and the term  $\alpha/(2c_0^2)$ in (7) therefore takes on a value of 0.5.

The proposed MSTM inherits from the original STM topology the improved noise behavior relative to the active commutating-mixer. For STM, the switches are connected to the common source terminals of the transconductor differential pairs. As a result, the noise current introduced by the switching devices appears as common-mode at the mixer output, which is rejected when the output voltage is taken differentially. Despite the topology differences of the MSTM in the LO path, the position of the switching stage relative to the transconductor stage of MSTM is the same as in the STM. Consequently, the noise current from switching devices in MSTM also cancels in the differential output. This effect is also revealed by (5) to (7), in which noise contributions from LO switches M<sub>5</sub>–M<sub>9</sub>, the feedback resistors  $R_F$ , the bias resistors  $R_B$  are absent. Thus, similar to STM, lower output noise  $(S_n)$  and NF is obtained with the MSTM.

The existence of  $L_G$  can further reduce the NF at high frequencies as depicted in (7). The calculated and simulated DSB NF curves of the mixer with and without  $L_G$  are also provided in Fig. 9(b). The simulation results are gotten with the IF output frequency kept constant at 250 MHz, i.e. the input RF frequency is swept in tandem with the LO frequency. As can be observed, the increase in NF at high frequency is diminished by  $L_G$  prominently. Quantitatively, the NF can be reduced by about 1 dB at around 10 GHz. A good agreement between the calculated and simulated NF can be observed too.

# C. IF Buffer

An IF output buffer following the proposed mixer is designed on chip. The purpose of having this buffer is to convert the mixer's differential IF port (IF+ and IF-) to a single-ended output, and to drive the relatively low impedance 50  $\Omega$  load in the testing. Since the mixer has sufficient gain to make the buffer's noise contribution negligible, this buffer is optimized for linearity performance.

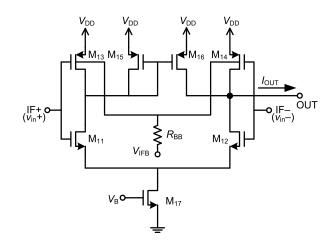

With these design considerations, an active current mirror with DS technique [8]–[11] is proposed to realize the IF output buffer, as can be seen in Fig. 7. The same schematic is redrawn in Fig. 10 for the convenience of discussion. The active current mirror is made of  $M_{11-12}$  and  $M_{15-17}$ , and body-biased auxiliary transistors  $M_{13-14}$  are added to cancel the third-order distortions and to improve the IP<sub>3</sub> performance of the buffer.

With the body terminals of  $M_{13-14}$  biased at 2.4 V, their body-source voltage and thus the threshold voltage are increased, which decreases their dc current for weak channel inversion. This changes the sign of the third-order transconductance of  $M_{13-14}$  from negative to positive, which is now opposite to that of the NMOS devices  $M_{11-12}$  (biased in strong inversion). Therefore the third-order distortion currents can be rejected upon summation at the outputs. With the assistance

Fig. 10. Circuit schematic of the proposed IF output buffer.

TABLE III Component Values for the IF Buffer

| Transistor | (W/L) 11,12   | (W/L) <sub>13,14</sub> | (W/L) <sub>15,16</sub> | (W/L) <sub>17</sub> |

|------------|---------------|------------------------|------------------------|---------------------|

| Size       | 30/0.12       | 110/0.12               | 250/0.12               | 60/0.4              |

| Component  | $R_{BB}$      |                        |                        |                     |

| Value      | 10 k $\Omega$ |                        |                        |                     |

TABLE IV Selected Simulation Results for Mixer Core & IF Buffer

| Mixer Gain |         | 1-dB Bandwidth | DSB NF   | IIP 3    |  |

|------------|---------|----------------|----------|----------|--|

| Core       | 19.5 dB | 1-10 GHz       | 4 - 5 dB | -0.7 dBm |  |

| IF         | Gain    | 3-dB Bandwidth | NF       | IIP 3    |  |

| Buffer     | -2 dB   | 5 GHz          | 8.8 dB   | 27.9 dBm |  |

of the two devices, the IIP3 of the buffer is improved from 16.1 dBm to 27.9 dBm.

The IF buffer has a 2 dB loss and 5 GHz 3-dB bandwidth at cost of 9.2 mA when driving a 50  $\Omega$  load. As the IF amplifier is cascaded with the mixer, its common-mode (CM) properties are also simulated. Without device mismatch, the gain from CM input to the output is less than -40 dB up to 500 MHz. Furthermore, with 10% mismatch added between the transconductor transistors M<sub>11</sub> and M<sub>12</sub>, the same gain is simulated to be less than -35 dB to 500 MHz. Considering the gain of the amplifier is -2 dB, a common-mode rejection ratio of more than 33 dB is acquired. The transistor dimensions and passive component values used are provided in Table III.

Simulations show that the IF buffer has a 3-dB bandwidth of 5 GHz, which substantially exceeds the IF output frequency band of the mixer (5 MHz to 500 MHz) chosen for this work and, therefore, the buffer has negligible to no impact on the frequency response of the mixer. Similarly, the IF buffer with an IIP<sub>3</sub> of +27.9 dBm introduces only a minimal to negligible degradation to the distortion behavior of the mixer core, which shows an IIP<sub>3</sub> of -0.7 dBm and a conversion gain of 19.5 dB. A summary of the mixer core and the IF output buffer's simulated behavior is shown in Table IV.

TABLE V

Summary of the Mixer's Performance in Comparison With Other Work

| Reference | CMOS    | Chip area          | DC power            | Gain      | Frequency | DSB NF               | OIP 3             | FOM             |

|-----------|---------|--------------------|---------------------|-----------|-----------|----------------------|-------------------|-----------------|

|           | process | (mm <sup>2</sup> ) | (mW)                | (dB)      | (GHz)     | (dB)                 | (dBm)             | (GHz)           |

| [3]       | 130 nm  | 0.315              | 34.5                | 17.5      | 1–5.5     | 3.9                  | 15.6              | 6.1             |

| [4]       | 130 nm  | 0.13               | 16.8                | 14        | 0.87–3.7  | 2.7 <del>-</del> 6.5 | 4.0 <sup>4</sup>  | 0.5             |

| [6]       | 180 nm  | 0.005              | 1.8                 | 12        | 1–4       | 21.5                 | 17                | 0.2             |

| [16]      | 130 nm  | 0.1 <sup>3</sup>   | 20                  | 11        | 1.0       | 15.9                 | 16.0              | 7.0             |

| [17]      | 180 nm  | 0.21 <sup>1</sup>  | 25.7 <sup>1</sup>   | 6.9       | 2–11      | 12.5 <sup>2</sup>    | 13.4 <sup>4</sup> | 0.5             |

| This Work | 130 nm  | 0.2                | 8.3+14 <sup>5</sup> | 15.5–17.5 | 1–10      | 4–5.2                | 16.5              | 11 <sup>6</sup> |

<sup>1</sup> Includes on-chip active wideband baluns.

<sup>2</sup> Estimated as single-sideband (SSB) NF minus 3 dB.

<sup>3</sup> With pads.

<sup>4</sup> Calculated as IIP<sub>3</sub>[dBm] + gain[dB].

<sup>5</sup> Power consumed by the mixer and the buffer, respectively.

<sup>6</sup> Mixer core + IF buffer. De-embedding simulated IF buffer data, the mixer core's FOM is estimated at 26.6.

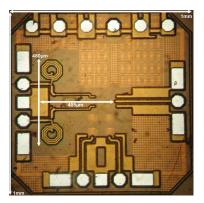

Fig. 11. Photograph of Broadband Mixer IC.

## **IV. MEASUREMENT RESULTS**

A photograph of the IC is shown in Fig. 11. It occupies a die area of 1 mm<sup>2</sup> including bonding pads, decoupling capacitors and the chip guard ring (plus chamfer regions), while the core circuit area is 405  $\mu$ m × 480  $\mu$ m. The chip consumes 22.3 mW of power from a 1.5 V supply, in which the mixer core costs 8.25 mW.

The broadband mixer IC was measured directly on-wafer using 40 GHz coplanar waveguide (CPW) probes and dc probes. A 50 GHz Keysight spectrum analyzer (E4448A) with the NF measurement software was used for gain, NF and linearity measurements. Off-chip bias-tee's and dc blocking capacitors were employed at the RF input and IF output respectively, in order to bias the IC and protect the measurement equipment. In addition, external 180° hybrids were used to provide differential RF and LO input signals from the single-ended sources. For all simulations and measurements, the LO power was fixed at -1 dBm, and the RF ( $f_{\rm RF}$ ), LO ( $f_{\rm LO}$ ) and IF ( $f_{\rm IF}$ ) frequencies were chosen such that  $f_{\rm RF} = f_{\rm LO} + f_{\rm IF}$ .

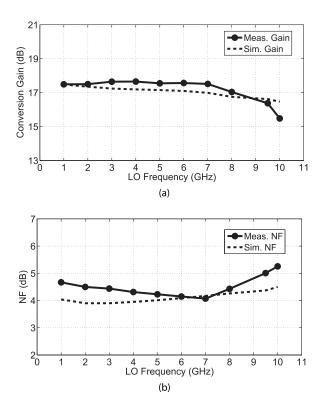

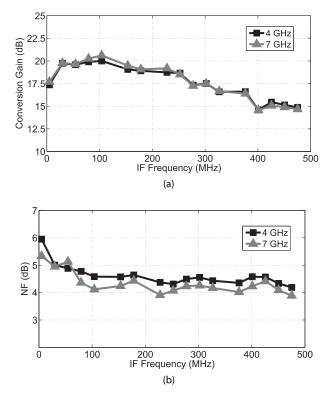

Fig. 12 shows the measured gain and DSB NF of the mixer versus LO frequency in comparison with the simulation results. In these measurements, the RF frequency was swept in tandem with the LO frequency, keeping the IF frequency fixed at 250 MHz. The measurements show that a high gain

Fig. 12. Measured mixer performance over LO frequency: (a) gain and (b) NF.

of 15.5–17.5 dB and a low NF of 4–5.2 dB are achieved from 1 GHz to 10 GHz. The NF is as low as 4 dB at 7 GHz. These results demonstrate that the RF 3-dB bandwidth of the mixer is quite wide, exceeding 10 GHz. There is good agreement between the measured and simulated results.

The gain and DSB NF of the mixer was also measured over a broad range of IF frequencies from 5 MHz to 500 MHz. Fig. 13 shows the results obtained at two different LO frequencies of 4 GHz and 7 GHz. A peak gain of 21 dB is achieved at IF frequencies below 100 MHz, and the IF 3-dB bandwidth is beyond 250 MHz. It should be noted that the drop in gain observed at 5 MHz is largely due to the relatively high cut-off frequency of the off-chip dc blocking capacitor ( $\approx$ 10 MHz).

Fig. 13. Measured mixer gain (a) and NF (b) versus IF frequency at LO frequencies of 4 GHz and 7 GHz.

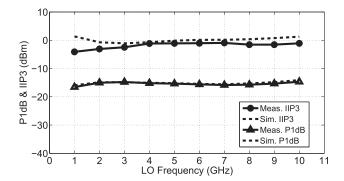

Fig. 14. P1dB and IIP3 versus LO frequency.

The linearity performance of the mixer was characterized from 1 GHz to 10 GHz. First, the measured 1-dB compression (P1dB) and two-tone third-order intercept (IP<sub>3</sub>) points are shown in Fig. 14. For these measurements, the RF frequency was swept in tandem with the LO frequency, keeping the IF frequency fixed at 250 MHz. The frequency spacing between the two tones for the IIP<sub>3</sub> measurement was 10 MHz. The measured P1dB reaches -14 dBm at 3 GHz and remains above -16 dBm out to 9 GHz. The IIP<sub>3</sub> peaks to -1 dBm around the center of the band, but drops to about -4.2 dBm towards the edges. To put the measured P1dB and IIP<sub>3</sub> performance in perspective, the simulated results are also shown in Fig. 14.

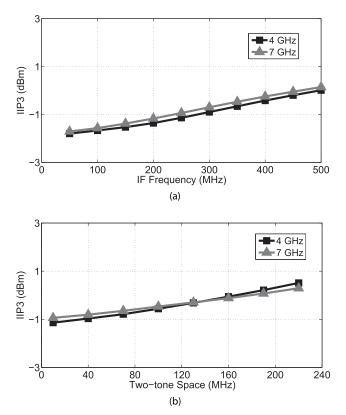

What is more, the sensitivities of IIP<sub>3</sub> performance to both IF frequency and two-tone spacing are measured. Fig. 15 shows the results measured at two LO frequencies of 4 GHz and 7 GHz. The sensitivities of IIP<sub>3</sub> to IF frequency is measured with the two-tone spacing is fixed at 10 MHz and the

Fig. 15. Sensitivities of  $IIP_3$  to (a) IF frequency (b) two-tone spacing at LO frequencies of 4 GHz and 7 GHz.

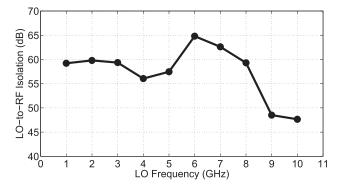

Fig. 16. Measured LO-to-RF isolation of the mixer.

IF frequency is swept from 50 MHz to 500 MHz. Within the whole range, the IIP<sub>3</sub> for both 4 and 7 GHz are within -2 dBm to 0.5 dBm. The sensitivities of IIP<sub>3</sub> to two-tone spacing is measured with one tone fixed at IF frequency of 250 MHz, and the other swept from 260 MHz to 470 MHz. The result shows that IIP<sub>3</sub> varies by less than 2 dB within the range.

Fig. 16 shows the measured LO-to-RF port isolation. The isolation is around 60 dB from 1 GHz to 8 GHz, and above 48 dB out to 10 GHz. Table V summarizes the proposed mixer's performance in comparison with other recently reported broadband CMOS mixers. For comparison, the figure of merit FOM commonly used in the literature for broadband amplifiers and mixers [18], [19] has been applied:

$$FOM[GHz] = \frac{BW[GHz] \times Gain[1] \times IIP3[mW]}{(NF[1]-1) \times P_{DC}[mW]}$$

$$= \frac{BW[GHz] \times OIP3[mW]}{(NF[1]-1) \times P_{DC}[mW]}$$

(8)

where BW [GHz] is the bandwidth in GHz, Gain [1] is the gain in magnitude, IIP3 [mW] is the input third-order intercept point in mW, OIP3 [mW] is the OIP<sub>3</sub> in mW, (NF [1] - 1) is the excess NF in magnitude, and  $P_{DC}$  [mW] is the dc power consumption in mW. FOMs calculated with the power of mixer core and the whole chip are both provided. As can be seen from Table V, the proposed mixer offers competitive performance over a broad bandwidth while consuming a small amount of power, thus featuring a high FOM compared to other work calculated in either way.

# V. CONCLUSION

A low-power, low-noise, wideband mixer in 0.13  $\mu$ m CMOS is presented in this paper. Based on STM structure, a transconductor stage with fixed DC operating point is switched by the ac-coupled LO signal. In this way, only a small LO signal is required to turn the transconductor on and off and thus a low-power LO buffer can be used to achieve 15.5–17.5 dB gain in 1–10 GHz bandwidth. As the noise power from LO stage appears in common mode at the mixer output, low NF of 4–5.2 dB is realized, too. The mixer core consumes a low power of 8.3 mW from 1.5-V supply, and the whole chip consumes 22.3 mW including the IF buffer. The active chip area is less than 0.2 mm<sup>2</sup>.

#### ACKNOWLEDGMENT

The authors acknowledge CMC Microsystems for fabrication services and support. Hao Li is a recipient of a doctoral scholarship from the China Scholarship Council (CSC).

#### REFERENCES

- A. Amer, E. Hegazi, and H. F. Ragaie, "A 90-nm wideband merged CMOS LNA and mixer exploiting noise cancellation," *IEEE J. Solid-State Circuits*, vol. 42, no. 2, pp. 323–328, Feb. 2007.

- [2] S. C. Blaakmeer, E. A. M. Klumperink, D. M. W. Leenaerts, and B. Nauta, "The blixer, a wideband balun-LNA-I/Q-mixer topology," *IEEE J. Solid-State Circuits*, vol. 43, no. 12, pp. 2706–2715, Dec. 2008.

- [3] S. S. K. Ho and C. E. Saavedra, "A CMOS broadband low-noise mixer with noise cancellation," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 5, pp. 1126–1132, May 2010.

- [4] D. Na and T. W. Kim, "A 1.2 V, 0.87–3.7 GHz wideband low-noise mixer using a current mirror for multiband application," *IEEE Microw. Wireless Compon. Lett.*, vol. 22, no. 2, pp. 91–93, Feb. 2012.

- [5] M. G. Kim, H. W. An, Y. M. Kang, J. Y. Lee, and T. Y. Yun, "A low-voltage, low-power, and low-noise UWB mixer using bulkinjection and switched biasing techniques," *IEEE Trans. Microw. Theory Techn.*, vol. 60, no. 8, pp. 2486–2493, Aug. 2012.

- [6] E. A. M. Klumperink, S. M. Louwsma, G. J. M. Wienk, and B. Nauta, "A CMOS switched transconductor mixer," *IEEE J. Solid-State Circuits*, vol. 39, no. 8, pp. 1231–1240, Aug. 2004.

- [7] S. Lee et al., "A broadband receive chain in 65 nm CMOS," in IEEE ISSCC Dig. Tech. Papers, Feb. 2007, pp. 418–612.

- [8] T. W. Kim, B. Kim, and K. Lee, "Highly linear receiver front-end adopting MOSFET transconductance linearization by multiple gated transistors," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 223–229, Jan. 2004.

- [9] A. M. El-Gabaly, D. Stewart, and C. E. Saavedra, "2-W broadband GaN power-amplifier RFIC using the *f<sub>T</sub>* doubling technique and digitally assisted distortion cancellation," *IEEE Trans. Microw. Theory Techn.*, vol. 61, no. 1, pp. 525–532, Jan. 2013.

- [10] T. H. Jin and T. W. Kim, "A 6.75 mW + 12.45 dBm IIP3 1.76 dB NF 0.9 GHz CMOS LNA employing multiple gated transistors with bulkbias control," *IEEE Microw. Wireless Compon. Lett.*, vol. 21, no. 11, pp. 616–618, Nov. 2011.

- [11] B.-K. Kim, D. Im, J. Choi, and K. Lee, "A highly linear 1 GHz 1.3 dB NF CMOS low-noise amplifier with complementary transconductance linearization," *IEEE J. Solid-State Circuits*, vol. 49, no. 6, pp. 1286–1302, Jun. 2014.

- [12] A. M. El-Gabaly, H. Li, and C. E. Saavedra, "A decade-bandwidth low-noise mixer RFIC with a distortion-canceling output amplifier," in *Proc. IEEE Int. Symp. RF Integr. Technol. (RFIT)*, Aug. 2016, pp. 1–3.

- [13] J. Kim, J.-K. Kim, B.-J. Lee, and D.-K. Jeong, "Design optimization of on-chip inductive peaking structures for 0.13-μm CMOS 40-Gb/s transmitter circuits," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 12, pp. 2544–2555, Dec. 2009.

- [14] T. H. Lee, *The Design of CMOS Radio-Frequency Integrated Circuits*, 2nd ed. New York, NY, USA: Cambridge Univ. Press, 2003.

- [15] M. T. Terrovitis and R. G. Meyer, "Noise in current-commutating CMOS mixers," *IEEE J. Solid-State Circuits*, vol. 34, no. 6, pp. 772–783, Jun. 1999.

- [16] M. Wang, S. He, and C. E. Saavedra, "+14 dB improvement in the IIP3 of a CMOS active mixer through distortion cancellation," in *Proc. IEEE Int. Wireless Symp.*, Apr. 2013, pp. 1–4.

- [17] P. Z. Rao, T. Y. Chang, C. P. Liang, and S. J. Chung, "An ultra-wideband high-linearity CMOS mixer with new wideband active baluns," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 9, pp. 2184–2192, Sep. 2009.

- [18] H. Zhang, X. Fan, and E. S. Sinencio, "A low-power, linearized, ultrawideband LNA design technique," *IEEE J. Solid-State Circuits*, vol. 44, no. 2, pp. 320–330, Feb. 2009.

- [19] M. Chen and J. Lin, "A 0.1–20 GHz low-power self-biased resistive-feedback LNA in 90 nm digital CMOS," *IEEE Microw. Wireless Compon. Lett.*, vol. 19, no. 5, pp. 323–325, May 2009.

Hao Li (M'14) received the B.Sc. degree in microelectronics, and the M.Sc. (Eng.) degree in integrated circuit design from Xi'an Jiaotong University, Xi'an, China, in 2010 and 2012, respectively. He is currently pursuing the Ph.D. degree with Queen's University, Kingston, ON, Canada. His research interests include RF CMOS frontend ICs. He served as the Vice-Chair of the AP-S/MTT-S Joint Chapter of the IEEE Kingston Branch from 2015 to 2016.

Ahmed M. El-Gabaly (S'07–M'12) received the B.A.Sc. degree in computer engineering from the University of Waterloo in 2005, and the M.Sc. (Eng.) and Ph.D. degrees in electrical engineering from Queen's University in 2007 and 2011, respectively. His Ph.D. thesis was on Novel Microwave CMOS Pulsed Circuits (pulse generators and LNAs) for UWB Automotive Radar. In 2011, he was a Post-Doctoral Fellow with the Gigahertz Integrated Circuits Group, Queen's University, undertaking research on linear broadband GaN power amplifiers.

He is currently an RFIC Design Engineer with Broadcom Corporation, designing 60-GHz transmitter RFICs in CMOS for high-speed wireless communications.

**Carlos E. Saavedra** (S'92–M'98–SM'05) received the B.Sc. degree in electrical engineering from the University of Virginia, Charlottesville, and the M.Sc. and Ph.D. degrees in electrical engineering from Cornell University, Ithaca, NY, USA. From 1998 to 2000, he was a Senior Engineer with Millitech Corporation. In 2000, he joined Queen's University, Kingston, ON, Canada, where he currently holds the rank of Professor. He served as the Graduate Chair for the Department of Electrical and Computer Engineering from 2007 to 2010.

Dr. Saavedra is a member of the TPRC of the IEEE International Microwave Symposium (IMS), steering and technical program committees of the 2012 IEEE IMS, and the IEEE RFIC Symposium TPC from 2008 to 2011. He is an Associate Editor of the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES. He served as the Section Chair of the Natural Sciences and Engineering Research Council of Canada Discovery Grants Evaluation Group from 2012 to 2014. He was the Chair of the IEEE MTT-S Technical Coordinating Committee 22 on Signal Generation and Frequency Conversion from 2010 to 2013.

He is a recipient of an NSERC Discovery Accelerator Award. He was voted third-year ECE Professor of the year with Queen's University in 2012 and 2013.