# 4.0–5.5 GHz Tunable Power Splitter RFIC using Active Inductors

You Zheng<sup>1</sup> and Carlos E. Saavedra<sup>2</sup>

<sup>1</sup>Formerly with Queen's University, now with SkyWave Mobile Communications, Ottawa, Ontario, Canada <sup>2</sup>Department of Electrical and Computer Engineering, Queen's University, Kingston, Ontario, Canada

Abstract—A highly compact and tunable four-port power splitter was designed and fabricated in a 180 nm CMOS process. Instead of distributed transmission lines, an LC lumped-element equivalent was selected for on-chip realization of the power splitter. To further reduce the varied by changing the bias current of the gyrator circuit. Experimental tests reveal that the power split is 6 dB and the center frequency can be tuned from 4.0 GHz to 5.5 GHz. The chip was biased from a 3 V dc voltage supply and consumes a maximum of 69 mW of power.

*Index terms*-active indcutors, active power splitters, power couplers, RFIC's, CMOS

### I. INTRODUCTION

In spite of the low cost of CMOS RF integrated circuits (RFIC's) compared to their III-V counterparts, there is a class of high-frequency circuits that remains prohibitively expensive to implement on-chip even in CMOS: passive microwave circuits. The basic problem is that the physical dimensions of distributed-element passive circuits such as power splitters, filters and baluns, for instance, are on the order of the signal wavelength. Thus, at the lower end of the microwave spectrum these circuits are too large for on-chip realization. As a result, passive microwave circuits are usually located off-chip, on a printed circuit board, which reduces the overall manufacturing throughput and yield for microwave systems.

One approach to bring low-frequency passive microwave components on-chip has been to reduce their size by converting the distributed-element circuits into lumped-element equivalents [1]–[4]. This lumped-element approach is attractive for circuits such as power splitters because, in many instances, inductors with moderate quality factors (Q's) can be used which are easier to implement in CMOS and other semicondor processes. Power splitters are ubiquitous circuits in high-frequency systems [5], [6] and their most common manifestation is the equal n-way splitter although unequal splitters [7]–[9] are also used.

This paper reports on the design and experimental verification of a lumped-element power splitter implemented in a standard 180 nm CMOS process. Through the use of active

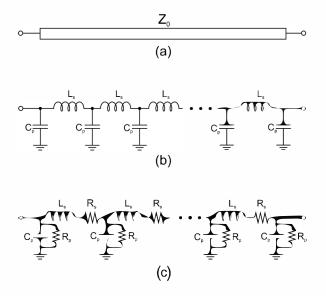

Fig. 1. (a) distributed transmission line and its (b) lossless and (c) lossy lumped-element equivalent circuit models.

inductors [10]–[13] instead of passive spiral inductors the size of the coupler was further reduced. The proposed power coupler's center frequency can be tuned from 4.0 GHz to 5.5 GHz while the splitter described in [3], also implemented in 180 nm CMOS, has a tuning range of 3.6 GHz to 4.7 GHz.

## **II. POWER SPLITTER CIRCUIT**

The distributed transmission line depicted in Fig. 1(a) can be modeled [14] with the lumped-element L-C ladder circuit in Fig. 1(b). If the dielectric material on which the transmission line rests is very pure and if a high-quality metal is used to implement the transmission line traces, then the lossless model in Fig. 1(b) can be used. For best accuracy, the lossy transmission line model in Fig. 1(c) is used because it accounts for the finite conductivity of the metal trace and the dielectric losses through resistances  $R_s$  and  $R_p$ , respectively. When the length of a transmission line is sufficiently short (i.e. less than one wavelength) then a truncated version of the lumped-

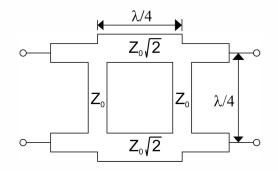

Fig. 2. Distributed-element microwave branchline power splitter.

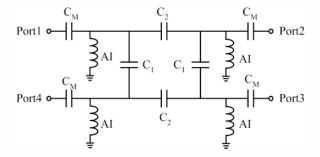

Fig. 3. Lumped-element realization of the branchline power splitter.

element networks can be used. The truncated model normally has three components and it is most accurate at the frequency at which the components are calculated.

A diagram of the microwave power splitter that was chosen for this work is shown in Fig. 2. Port 1 is the input port, Ports 2 and 3 are the signal transmission ports and Port 4 is isolated. Each  $\lambda/4$  segment of transmission line was replaced with a three-component equivalent circuit and the result is the circuit in Fig. 3. For simplicity, and to reduce area, all parallel components sharing a single node were merged into a single component. Note that while the equivalent transmission models in Fig. 1 have series inductances and shunt capacitors, the circuit in Fig. 3 has shunt inductors and series capacitors. This reversal was carried out through a  $Y \leftrightarrow \Delta$  circuit transformation.

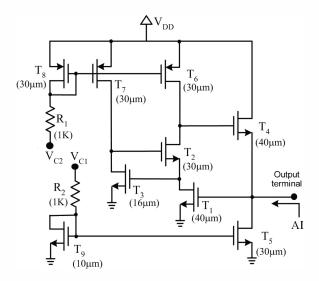

The series capacitors  $(C_M)$  at the port terminals serve as dc blocks and also help with input impedance matching. The capacitances C<sub>1</sub> and C<sub>2</sub> were implemented using MOS varactors so that their values could be optimized for best phase and amplitude balance in the power splitter. For this design, the capacitor values were:  $C_M = 0.4$  pF,  $C_1 = 0.2$  pF,  $C_2$ =  $1.414 C_1$  The lumped-element inductors were implemented using the transistor-based circuit shown in Fig. 4. The active inductor saves chip area compared to a spiral inductor and its inductance value can be changed by varying its bias current. At 4.75 GHz, the center frequency of the power splitter's tuning range, the active inductors had a value of 1.4 nH. The ability to simultaneously vary the capacitances  $C_1 \mbox{ and } C_2 \mbox{ plus the }$ inductances allows the center frequency of the power splitter to be tuned over a very broad frequency range of 1.5 GHz between 4.0 GHz and 5.5 GHz.

Fig. 4. Actrive inductor circuit topology realized in 180 nm CMOS.

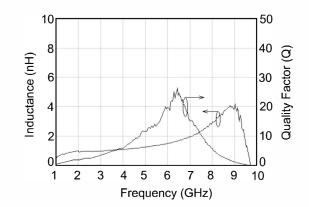

Fig. 5. The active inductor's measured inductance versus frequency.

The topology used for the active inductor in Fig. 4 has two feedback loops: transistors  $T_1/T_2/T_4$  make up the first loop and transistors  $T_2/T_3$  make up the second loop. The two loops are joined at transistor  $T_2$ . This dual loop arrangement improves the frequency response of the active inductor compared to configurations that rely on a single loop topology [10]. DC current is supplied to the active inductor through a pair of current mirrors. The mirror currents are controlled through the voltages  $V_{C1}$  and  $V_{C2}$ .

#### **III. EXPERIMENTAL RESULTS**

A chip was fabricated to test the active inductor performance by itself and another chip was fabricated to test the performance of the power splitter. Both chips were fabricated using a standard 180 nm CMOS process.

The plot in Fig. 5 shows the measured inductance and quality factor of the active inductor as a function of frequency. This active inductor was designed to produce an inductance of 1 nH, which is maintained over a span of nearly 5 GHz. The maximum inductance is 4 nH at 9 GHz and its self-resonant

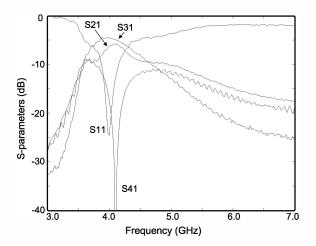

Fig. 6. Measured s-parameters at the lower-end of the band.

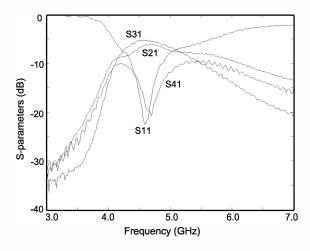

Fig. 7. Measured s-parameters at mid-band.

frequency is 9.8 GHz. The quality factor of this inductor peaks at around 20 at 6.4 GHz. Active inductors often have much better Q's than passive inductors because they can be designed to have a very small accompanying parasitic resistance. The parasitic resistance can even be negative in which case it can be used in conjunction with a capacitor to create an oscillator.

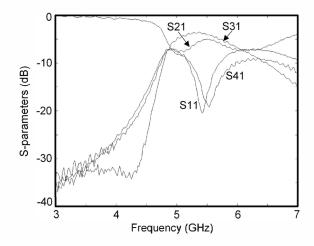

Figures 6, 7, and 8 show the measured s-parameters of the power splitter at 4 GHz, 4.75 GHz and 5.5 GHz, respectively. For all three cases, the forward transmission coefficients,  $S_{21}$  and  $S_{31}$ , are close to -6 dB. Ideally, the transmission coefficients should be -3 dB, but in this splitter the additional 3 dB drop comes from the MOS varactors and losses in the active inductors. Increasing the transistor dimensions in the active inductors can reduce their loss but the tradeoff would be a lower center frequency for the overall circuit. The power splitter's reflection coefficient at the input port,  $S_{11}$ , and the isolation between ports 1 and 4,  $S_{41}$ , are around -20 dB or lower. At the center frequency of 4.75 GHz, the active inductor's internal bias voltages in the power splitter,  $V_{C1}$  and  $V_{C2}$ , were set to 1.1 V and 0.44V, respectively.

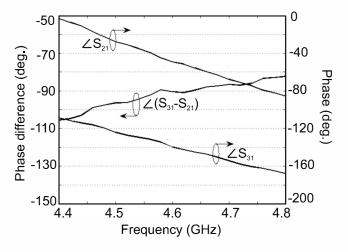

The phase response of the power splitter was measured at

Fig. 8. Measured s-parameters at the upper-end of the band.

Fig. 9. Measured phase response at mid-band.

different center frequencies. The plot in Fig. 9 shows  $\angle S_{21}$ ,  $\angle S_{31}$  and  $\angle (S_{21}-S_{31})$  when the splitter was tuned to 4.75 GHz. As expected for a quadrature power splitter  $\angle (S_{21}-S_{31})$  is in the neighborhood of 90°.

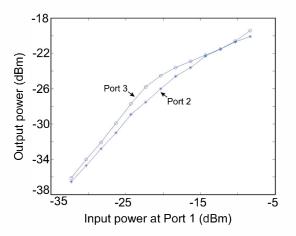

The plot in Fig. 10 shows the input power versus output power response of the splitter. The input 1-dB compression point ( $IP_{1dB}$ ) of this splitter is -20 dBm when the output power is measured at port 2 and -18 dBm when the output is measured at port 3. In active power splitters the linearity is limited by the active inductors, a feature also observed in the circuit reported in [3].

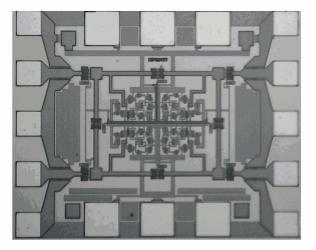

A microphoto of the fabricated chip is shown in Fig. 11.

## **IV. CONCLUSION**

Traditional high-frequency power splitters using distributed elements require a large area because their size is proportional to the signal's wavelength. To reduce the size of a power splitter so that it can be placed on-chip a lumped-element realization of a microwave power splitter was designed and

Fig. 10. Measured input power versus output power response of the splitter.

Fig. 11. Microphotgraph of the power coupler chip

fabricated using a 180 nm CMOS process. Instead of passive spiral inductors, active inductors were used to further reduce the area footprint of the power splitter. Using the active inductor also allows for frequency tunability which is not possible when using passive power splitters.

## V. ACKNOWLEDGMENTS

This work was supported, in part, by a grant from the Natural Sciences and Engineering Research Council (NSERC) of Canada. The authors would like to thank CMC Microsystems, Kingston, Ontario, Canada, for chip fabrication services.

## References

- R. Vogel, "Analysis and design of lumped- and lumped-distributedelement directional couplers for mic and mmic applications," *IEEE Transactions on Microwave Theory and Techniques*, vol. 40, no. 2, pp. 253–262, Feb 1992.

- [2] W.-S. Tung, H.-H. Wu, and Y.-C. Chiang, "Design of microwave wideband quadrature hybrid using planar transformer coupling method," *IEEE Transactions on Microwave Theory and Techniques*, vol. 51, no. 7, pp. 1852–1856, July 2003.

- [3] H.-H. Hsieh, Y.-T. Liao, and L.-H. Lu, "A compact quadrature hybrid mmic using cmos active inductors," *IEEE Transactions on Microwave Theory and Techniques*, vol. 55, no. 6, pp. 1098–1104, June 2007.

- [4] I. Bahl, "Ultrabroadband and compact power dividers/combiners on gallium arsenide substrate," *IEEE Microwave Magazine*, vol. 9, no. 2, pp. 96–104, April 2008.

- [5] S. Winter, A. Koelpin, and R. Weigel, "Six-port receiver analog frontend: Multilayer design and system simulation," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 55, no. 3, pp. 254–258, March 2008.

- [6] H.-C. Chen, T. Wang, H.-W. Chiu, Y.-C. Yang, T.-H. Kao, G.-W. Huang, and S.-S. Lu, "A 5-ghz-band cmos receiver with low lo self-mixing front end," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 56, no. 4, pp. 705–713, April 2009.

- [7] H. Oraizi and A.-R. Sharifi, "Optimum design of asymmetrical multisection two-way power dividers with arbitrary power division and impedance matching," *IEEE Transactions on Microwave Theory and Techniques*, vol. 59, no. 6, pp. 1478–1490, June 2011.

[8] Y.-L. Wu, H. Zhou, Y.-X. Zhang, and Y.-A. Liu, "An unequal wilkinson

- [8] Y.-L. Wu, H. Zhou, Y.-X. Zhang, and Y.-A. Liu, "An unequal wilkinson power divider for a frequency and its first harmonic," *IEEE Microwave* and Wireless Components Letters, vol. 18, no. 11, pp. 737–739, Nov. 2008.

- [9] S. Yang and A. Fathy, "Synthesis of an arbitrary power split ratio divider using substrate integrated waveguides," in *IEEE International Microwave Symposium Digest*, June 2007, pp. 427–430.

- [10] Y. Zheng and C. E. Saavedra, "Frequency response comparison of two common active inductors," *Progress in Electromagnetics Research Letters*, vol. 113, pp. 113–119, 2010.

- [11] J. Xu, C. Saavedra, and G. Chen, "An active inductor-based vco with wide tuning range and high dc-to-rf power efficiency," *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 58, no. 8, pp. 462–466, Aug. 2011.

- [12] Y. Zheng and C. Saavedra, "Feedforward-regulated cascode ota for gigahertz applications," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 55, no. 11, pp. 3373–3382, Dec. 2008.

- [13] R. Geiger and E. Sanchez-Sinencio, "Active filter design using operational transconductance amplifiers: A tutorial," *IEEE Circuits and Devices Magazine*, vol. 1, no. 2, pp. 20–32, Mar. 1985.

- [14] J. Hagen, *Radio-Frequency Electronics: Circuits and Applications*, 2nd ed. New York: Cambridge University Press, 2009.